biblioteka@mondragon.edu

This is an Accepted Manuscript version of the following article, accepted for publication in:

A. Fernandez-Hernandez, A. Garcia-Bediaga, I. Villar and G. Abad, "Analytical Model of the Current Stress in Active-Bridge Active-Clamp Converter for More Electric Aircraft," 2021 IEEE Energy Conversion Congress and Exposition (ECCE), 2021, pp. 1785-1792.

https://doi.org/10.1109/ECCE47101.2021.9595016

© 2021 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

# Analytical Model of the Current Stress in Active-Bridge Active-Clamp Converter for More Electric Aircraft

Alejandro Fernandez-Hernandez, Asier Garcia-Bediaga, Irma Villar

Power Electronics Area Ikerlan Technology Research Centre Basque Research and Technology Alliance (BRTA) Arrasate/Mondragon, Spain alejandro.fernandez@ikerlan.es Gonzalo Abad Electronics and Computing Department Mondragon Unibertsitatea Arrasate/Mondragon, Spain

Abstract-Nowadays, the emergence of electrically supplied actuators and energy storage systems is leading the aeronautic industry to develop aircrafts with more electrical power installed. Therefore, different Power-Electronic Converters (PECs) have been proposed to satisfy the requirements of More Electric Aircraft (MEA) applications. Among them Active-Bridge-Active-Clamp converter is one of the most promising isolated DC/DC PEC topologies. To expand the characterization of this PEC, the analytical model to determine the root mean square and average currents in secondary power devices is presented in this work when working with single-phase shift rectangular modulation. Furthermore, a simulation model is developed in PLECS to validate the analytical model proposed in this work in MEA scenarios. Finally, the simulation model is employed to determine the error caused by dead time and clamp capacitances in the currents that are calculated analytically.

*Index Terms*—DC-DC Power Conversion, Active-Bridge-Active-Clamp, Analytical Modelling, More Electric Aircraft.

### I. INTRODUCTION

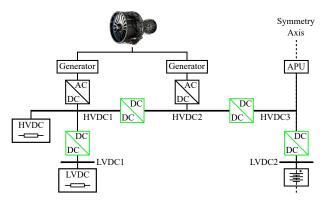

In last years, the electrification of the aircraft has experienced a large increment in R&D effort. The aim is to reduce the environmental impact and to improve passenger safety and comfort. Bidirectional isolated DC/DC Power Electronic Converters (PECs) play an important role in new electric power distribution networks proposed for More Electric Aircraft (MEA) [1]. In MEA electric power distribution networks, these DC/DC PECs are mainly found in energy storage systems and/or power flow regulation among DC buses, as shown in Fig. 1. In this context, Dual-Active-Bridge (DAB) converter, first presented in [2], has been studied in literature considering different modulation methods [3] and switches thermal behavior [4]. However, main disadvantage of DAB converter is the required large capacitance to satisfy the low voltage ripple requirement in some MEA applications (e.g. interfacing High Voltage DC (HVDC) and Low Voltage DC (LVDC) buses).

As an alternative to DAB, Active-Bridge-Active-Clamp (ABAC) converter has been proposed to solve this issue [5]. In this converter, the secondary stage is modified by including clamp capacitances and output inductances. Since

Fig. 1. Distributed electric power distribution network in MEA. The ilustration is focused on the DC distribution network for hybrid and electric aircraft.

secondary half-bridge branches work at 50 % of duty cycle and are complementary switched, these inductances are in phase oposition, and thus the resulting ripple on the LVDC bus is cancelled. DAB and ABAC converters have been compared in literature in terms of volume, weight and efficiency [6], [7]. Furthermore, ABAC converter has been studied considering advanced modulation methods, as trapezoidal or triangular modulations [8], [9], which improve the converter performance when working outside nominal input and/or output voltage at low power transfer. Moreover, the influence of the mismatch of different design parameters on the output characteristics, as current sharing or voltage ripple cancelation, can be found in literature [10]. The behavior of the primary stage in ABAC is the same as in DAB, whose analytical model for the current stress has been developed in [11] for different modulation methods. Therefore, the analytical model of the currents in the secondary stage of ABAC converter is presented in this work. Based on these equations, the current stress in the switching devices can be compared in any case study. Moreover, these equations are useful in the sizing of switching devices and cooling system.

This work is organized as follows. The working principle

of ABAC converter when working with Single-Phase Shift (SPS) rectangular modulation is exposed in section II. In section III, the validation of the proposed analytical model is carried out by developing a simulation model in PLECs. Moreover, the relative error considering clamp capacitances and dead time variations is calculated in this section. Finally, main conclusions of this work are gathered in section IV. In the appendix, the analytical model of the Root Mean Square (RMS) and Average (AVG) currents is presented.

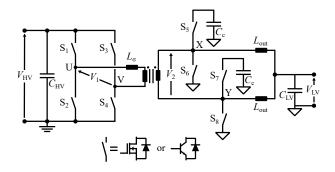

## II. SPS RECTANGULAR MODULATION IN ABAC CONVERTER

The schematic of ABAC converter is shown in Fig. 2. It is formed by a full-bridge in the primary stage and two half-bridge branches in the secondary side, which can act as inverter and/or rectifier connected through an isolation transformer. Semiconductors  $S_1 - S_4$  and  $D_1 - D_4$  connect the primary side of the transformer with the HVDC bus, while the secondary side is connected through  $S_5 - S_8$  and  $D_5 - D_8$  to the clamp capacitances ( $C_c$ ) and the output inductances ( $L_{out}$ ). These output inductances act as interface between the secondary half-bridges and the LVDC bus.

Among the different modulation methods that can be implemented on this topology, SPS rectangular modulation is the simplest and the most commonly used. Therefore, the analytical model of the RMS and AVG currents in secondary switching devices of ABAC converter when working with this modulation method is presented in this section.

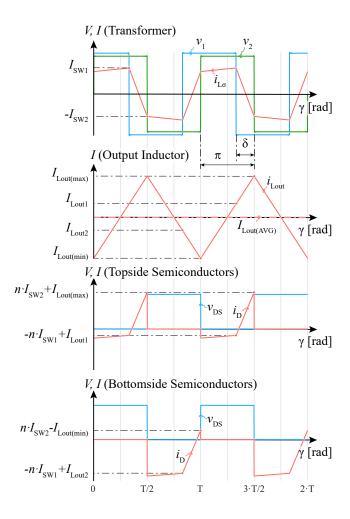

In Fig. 3, voltage waveforms in primary  $(v_1)$  and secondary  $(v_2)$  windings of the power transformer togheter with current waveform through the decoupling inductor  $(i_{L\sigma})$  are depicted. Furthermore, the current through output inductor  $(i_{Lout})$  is exposed. Looking at the configuration of the secondary side in ABAC converter, RMS and AVG currents in secondary switching devices depend on the currents that flow through the secondary winding of the power transformer and through the output inductors. After applying Kirchhoff current law in nodes X and Y (see Fig. 2), the current distribution in the power devices of this stage is obtained. Moreover, the current through topside (S<sub>5-7</sub> and D<sub>5-7</sub>) and bottomside (S<sub>6-8</sub> and D<sub>6-8</sub>) semiconductors is not the same, as it is shown in Fig. 3. In order to characterize the RMS and AVG current stress in

Fig. 2. Bidirectional isolated DC/DC ABAC converter for MEA.

Fig. 3. Main waveforms in secondary side of ABAC converter under SPS rectangular modulation. From top to bottom: Voltage in primary  $(v_1)$  and secondary  $(v_2)$  windings of the power transformer and current through decoupling inductor  $(i_{L\sigma})$ , current through output inductor  $(i_{Lout})$ , and blocking voltage  $(v_{DS})$  and drain current  $(i_D)$  in topside semiconductors  $(S_{5-7} \text{ and } D_{5-7})$ , and in bottomside semiconductors  $(S_{6-8} \text{ and } D_{6-8})$ . These waveforms are obtained assuming ideal clamp capacitors.

these devices, the current levels at  $(\pi - \delta)$  and switching instants are defined as A,B,C,D in (1) and (3) to simplify the mathematical development of this work:

$$A = (I_{\text{Lout}(\text{max})} + n I_{\text{sw2}}) , \qquad (1)$$

$$B = (I_{\text{Lout(min)}} - n I_{\text{sw2}}) , \qquad (2)$$

$$C = (I_{\text{Lout1}} - n I_{sw1}) , \qquad (3)$$

$$D = (I_{\text{Lout2}} + n I_{\text{sw1}}) , \qquad (4)$$

where *n* is the transformer turns ratio,  $I_{sw1}$  and  $I_{sw2}$  are the current values in the primary winding of the power transformer at switching instant of primary and secondary power devices,  $I_{Lout(max)}$  and  $I_{Lout(min)}$  are the maximum and minimum

current values in the output inductance, and  $I_{\text{Lout1}}$  and  $I_{\text{Lout2}}$  are the current in the output inductance at switching instant in primary side. The equations to determine these currents are presented in (5)-(10):

$$I_{\rm sw1} = \frac{V_{\rm HV} \,\pi + n \, V_{\rm Clamp} \left(2 \, |\delta| - \pi\right)}{4 \,\pi \, f_{\rm sw} \, L_{\sigma}} \quad , \tag{5}$$

$$I_{\rm sw2} = \frac{V_{\rm HV} \left(2 \ |\delta| - \pi\right) + n \, V_{\rm Clamp} \, \pi}{4 \, \pi \, f_{\rm sw} \, L_{\sigma}} \quad , \tag{6}$$

$$I_{\rm Lout(max)} = I_{\rm Lout(AVG)} + 0.5 \,\Delta I_{\rm Lout(pk-pk)} \quad (7)$$

$$I_{\rm Lout(min)} = I_{\rm Lout(AVG)} - 0.5 \,\Delta I_{\rm Lout(pk-pk)} \quad , \qquad (8)$$

$$I_{\text{Lout1}} = I_{\text{Lout(min)}} + \frac{\left(I_{\text{Lout(max)}} - I_{\text{Lout(min)}}\right)}{\pi} (\pi - \delta),$$

(9)

$$I_{\text{Lout2}} = I_{\text{Lout(max)}} + \frac{\left(I_{\text{Lout(min)}} - I_{\text{Lout(max)}}\right)}{\pi} (\pi - \delta),$$

(10)

where  $V_{\rm HV}$  is the voltage on the HVDC bus,  $V_{\rm Clamp}$  is the voltage on the clamp capacitances ( $V_{\rm Clamp} = 2 V_{\rm LV}$ ),  $f_{\rm sw}$  is the switching frequency and  $L_{\sigma}$  is the decoupling inductance. Furthermore, current ripple ratio ( $r_{\rm I}$ ), peak-to-peak current ripple ( $\Delta I_{\rm Lout(pk-pk)}$ ) and AVG current ( $I_{\rm Lout(AVG)}$ ) in the output inductance are defined in (11)-(13):

$$I_{\rm Lout(AVG)} = \frac{P_{\rm out}}{V_{\rm Clamp}},$$

(11)

$$\Delta I_{\rm Lout(pk-pk)} = \frac{V_{\rm LV}}{2L_{\rm out}f_{\rm sw}},\tag{12}$$

$$r_{\rm I} = \frac{\Delta I_{\rm Lout(pk-pk)}}{I_{\rm Lout(AVG)}} = \frac{\left(V_{\rm LV}\right)^2}{L_{\rm out} f_{\rm sw} P_{\rm out}}.$$

(13)

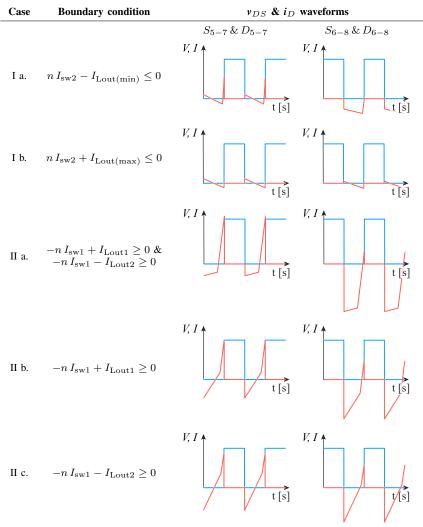

TABLE I

Summary of ZVS and HS cases, boundary conditions and voltage and current waveforms in power devices (Forward mode).

Different operating modes are defined for ABAC converter in order to differenciate if the current is flowing through switch or diode. Furthermore, this operating modes describe hardswitching (case I) and zero-voltage-switching (case II), divided in case I a, case I b, case II a, case II b and case II c. These distinctions in case I and case II are done to differenciate whether the current level is possitive or negative at  $\pi$  and  $(\pi - \delta)$  instants respectively in topside and bottomside power devices. The corresponding boundary conditions are presented in Table I together with the blocking voltage and drain current waveform of each operating mode.

Then, RMS and AVG current equations are obtained for topside and bottomside semiconductors in each operating mode. The analytical models of the defined operating modes are presented in Tab. III-VI, which are gathered in the appendix of this work. Furthermore, the required modifications to calculate the RMS and AVG currents in secondary switching devices in backward mode, i.e. LV to HV power transfer, are described in the appendix based on the presented analytical models.

#### **III. SIMULATION ANALYSIS**

To validate the analytical model proposed in this work, a simulation model is developed in PLECS. The design values considered in this work are gathered in Table II based on typical MEA specifications [5]. Furthermore, the values of clamp capacitance and dead time utilized in this section to determine the error when considering non-idealities are also presented.

TABLE II MEA DESIGN PARAMETERS

| Parameter          | Value  | Units            |  |

|--------------------|--------|------------------|--|

| $V_{\rm HV}$       | 270    | V                |  |

| V <sub>LV</sub>    | 28     | V                |  |

| n                  | 5      | -                |  |

| $P_{\mathrm{out}}$ | 10     | kW               |  |

| $F_{sw}$           | 100    | kHz              |  |

| $L_{\sigma}$       | 7.56   | $\mu \mathrm{H}$ |  |

| $L_{\rm out}$      | 3      | $\mu$ H          |  |

| $C_{\rm c}$        | 25-300 | $\mu$ F          |  |

| $t_{ m dt}$        | 50-350 | ns               |  |

#### A. Validation based on simulation

In order to simplify the validation procedure, the following assumptions are taken. To idealize the simulation model, dead time in switching devices and conduction losses in passive devices are not considered. Moreover, clamp capacitances are modeled as ideal voltage sources.

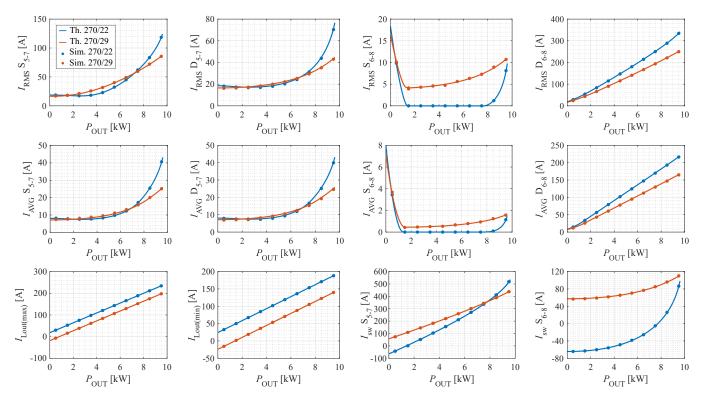

In Fig. 4, RMS and AVG currents in topside and bottomside switching devices are depicted in two MEA scenarios, i.e.  $V_{LV} = 22$  V and  $V_{LV} = 29$  V. At high power transfer, higher currents are expected in all semiconductors when working with low voltage in LVDC bus. In topside semiconductors, the current stress is similar in both cases at medium and low power transfer. However, this is not the case of bottomside semiconductors. In these semiconductors, the current level in diodes is higher at 22 V in LVDC bus in the whole output power

Fig. 4. Switching, RMS and AVG currents in secondary switching devices  $S_5 - S_8$  and  $D_5 - D_8$  together with maximum and minimum current in the output inductors in ABAC converter (at  $V_{HV}$ =270 V,  $F_{sw}$ =100 kHz,  $L_{\sigma}$ =7.56  $\mu$ H,  $L_{out}$ =3  $\mu$ H and n=5), when  $V_{LV}$ =29 V and/or  $V_{LV}$ =22 V

range. In  $S_{6-8}$ , the worst case occurs at high output voltage, due to the fact that no current flows through these switches when working in case I a. Furthermore, it is noticeable that the worst operating condition in these semiconductors is found at zero power transfer. This fact repercutes on the corresponding conduction losses of these power devices at low power transfer.

To provide a complete validation of the equations included in this paper, the maximum and minimum current level through the output inductor and switching currents in topside and bottomside semiconductors are also presented. Both maximum and minimum currents in  $L_{out}$  are defined by the same slope. Moreover, the higher secondary switching currents expected in topside semiconductors compared to bottomside devices are observed.

To validate the accuracy of the equations included in this work, theoretical values are presented toghether with simulation results. A good correlation between analytical and simulation results of the RMS and AVG currents is exposed in Fig. 4, validating the analytical models presented in this work.

#### B. Impact of clamp capacitances and dead time

The simplifications assumed in previous steps facilitate the mathematical development to obtain the analytical model presented in this work. However, the expected RMS and AVG currents are affected by clamp capacitances and dead time. In order to analyze the impact of these non-idealities, the relative error ( $\varepsilon_{rel}$ ) of the analytical models is calculated with the developed simulation model.

First, the clamp capacitance is swept from 25-300  $\mu$ F to study the deviations of the analytical model when clamp capacitor peak-to-peak voltage ripple ( $\Delta V_{\text{Clamp}(pk-pk)}$ ) is varied. These capacitances correspond to 11.5 V (25  $\mu$ F) and 0.25 V (300  $\mu$ F) of  $\Delta V_{\text{Clamp}(pk-pk)}$ . The required capacitance to obtain the desired  $\Delta V_{\text{Clamp}(pk-pk)}$  is computed with (14):

$$C_{\rm c} = \frac{C A \delta}{2 \pi f_{\rm sw} \Delta V_{\rm Clamp(pk-pk)} (A-C)}$$

(14)

Second, the dead time  $(t_{\rm dt})$  is presented for 50 ns and 500 ns, which correspond to 0.5 % and 5 % of the switching frequency selected in this work, i.e.  $f_{\rm sw} = 100$  kHz.

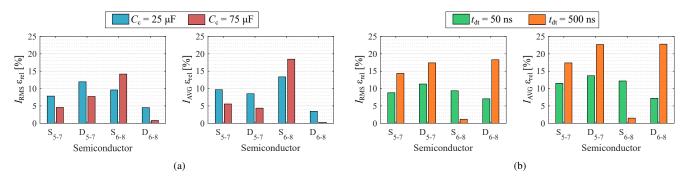

In Fig. 5, the relative error in LV side semiconductors of the analytical models developed in this work is presented for  $V_{\rm LV} = 29V$  at maximum power transfer. The impact of clamp capacitance variations is depicted in Fig. 5(a). In both RMS and AVG currents,  $\varepsilon_{\rm rel}$  tends to decrease as higher is the clamp capacitance. This is due to the fact that the resulting  $\Delta V_{Clamp(pk-pk)}$  is inversely proportional to the clamp capacitance. Thus, the difference between analytical and simulation results are lower as higher is this capacitance. In the case of S<sub>6-8</sub> bottomside semiconductors, the relative error shown is caused by the short time interval in which the current is flowing through these semiconductors at high-power transfer.

When considering dead time variations [see Fig. 5(b)],  $\varepsilon_{\rm rel}$  increase as higher is the selected dead time in all semiconductors. As same as in capacitance variations, the tend in  $S_{6-8}$  is inverse to the expected, which is also caused by the sensitivity of these semiconductors to the variation of the dead time. Furthermore, it is noticeable that the impact of the dead time in the presented analytical models is higher than clamp capacitance since the accuracy of the equations is considerable lower when dead time is increased.

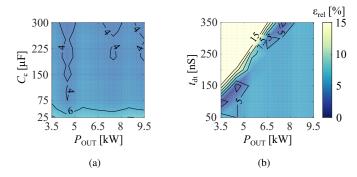

In order to completely characterize the limitations of the analytical models, the relative error is also studied for output power variations from 35%-95% of the maximum output power. Therefore,  $\varepsilon_{\rm rel}$  map is presented in Fig. 6 to study the impact of clamp capacitance and dead time variations on the RMS currents of  $S_{5-7}$  semiconductors. Considering the impact of the  $C_{\rm c}$  shown in Fig. 6(a), it is noticeable that the accuracy of the models is good. However, this accuracy is worst as lower is the clamp capacitance in the whole output power range. In this work, the maximum relative error of topside semiconductors is 15 % for 25  $\mu$ F of clamp capacitance, that corresponds to  $\Delta V_{

m Clamp(pk-pk)} = 11$  V, i.e. 20 % of the voltage in the clamp capacitance. Furthermore,  $t_{\rm dt}$  influence is presented in Fig. 6(b). The results show a good agreement between analytical and simulation when working at low dead time in the considered output power range. However, there is a limitation of the analytical models when the output power is decreased or the dead time increased, i.e. the area where  $\varepsilon_{\rm rel}$ is higher than 15 %.

Then, the analysis of the ABAC converter with the presented analytical models must be carefully checked when

Fig. 5. Relative error ( $\varepsilon_{rel}$ ) bar chart of the analytical models presented in this paper working at  $V_{LV}$ =29 V and maximum power transfer in forward mode for: a) clamp capacitances and b) dead time variations.

Fig. 6. Relative error ( $\varepsilon_{\rm rel}$ ) map of the analytical models presented in this paper in topside  $S_{5-7}$  power devices when  $V_{\rm LV}$ =29 V in the whole output power range for: a) clamp capacitances and b) dead time variations.

working under these conditions. The impact of varying clamp capacitance and dead time in ABAC converter has been presented to find the limitations of the equations included in this work. The accuracy of the models shows to be good when  $\Delta V_{\text{Clamp}(pk-pk)}$  is set below 20 % of the voltage in  $C_c$ . Nevertheless, this is not the case of dead time influence, whose increment considerably increase the resulting error especially when working at low power transfer.

#### **IV. CONCLUSION**

In this work, analytical models of the RMS and AVG currents in secondary switching devices in ABAC converter have been obtained. To this end, SPS Rectangular modulation is considered for the study since it is the simplest and easiest to implement. Based on the presented models, RMS and AVG currents in the aforementioned switching devices in both forward and backward power transfer can be calculated.

The results obtained with the simulation model developed in PLECS validate the analytical model in a MEA scenario, considering the highest and lowest voltages on LVDC side. The behavior of topside semiconductors shows to be similar in the considered cases. However, the current stress in bottomside switches is higher when the output voltage is increased. Furthermore, large current levels flow through diodes when the output voltage is lower.

To analyze the non-idealities of the analytical model, as clamp capacitances and dead time in power devices, on the resulting RMS and AVG currents from the analytical models, the relative error compared to the simulation model has been presented for secondary semiconductors working at maximum power transfer. At this power transfer level, the accuracy of the equations show to be good when varying clamp capacitance and/or dead time. However, the error presented in bottomside semiconductors  $S_{6-8}$  is above 15 %. This is due to the short time in which the current is flowing through these semiconductors, being the influence of the non-idealities higher on them. Furthermore, the error is analyzed for different output power levels in order to see the limitations of the models. The worst agreement between analytical equations and simulation model is found when the dead time is increased at low-power transfer.

The validation of these equations allows its utilization in the sizing of power devices and cooling system. Furthermore, this work is useful for optimization routines for the design of ABAC PEC for different application proposals, where the high computational cost of the simulation model is avoided.

## APPENDIX RMS AND AVG EQUATIONS IN SECONDARY POWER DEVICES

In Tables III, IV, V and VI, the equations of the RMS and AVG currents are summarized. Each case correspond to an operating mode of ABAC, which are described in section II. Case II b. is not found in tables since the equations that describe its behavior are obtained from cases II a (for bottomside semiconductors) and II c (for topside semiconductors).

Furthermore, the presented models can be utilized for forward (HV to LV power transfer) and backward (LV to HV power transfer) operating modes. However, some adaptations must be done in order to adapt these models to backward operation. When the converter works in backward mode, the sign of the current waveform is the opposite of the forward mode. Therefore, the RMS and AVG current stress are calculated by swapping the equations of  $S_{5-7}$  with  $D_{5-7}$ , and  $S_{6-8}$  with  $D_{6-8}$  in each operating mode.

| Switch           | RMS                                                                                                                                                               | AVG                                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $S_{5-7}$        | $\sqrt{\left(rac{1}{T_{ m sw}} ight) rac{A^3}{3\left(A-C ight)} T_{\delta}}$                                                                                    | $\left(\frac{1}{T_{\rm sw}}\right) \frac{A^2}{2 (A-C)} T_{\delta}$                                                                                                 |

| $S_{6-8}$        | $\sqrt{\left(rac{1}{T_{ m sw}} ight) rac{B^3}{3\left(B-D ight)} T_{\delta}}$                                                                                    | $\left(rac{1}{T_{ m sw}} ight)  rac{B^2}{2  \left(B-D ight)}  T_{\delta}$                                                                                        |

| $D_{5-7}$        | $\sqrt{\left(\frac{1}{T_{\rm sw}}\right)\left(\left(\frac{(C-B)^2}{3}+BC\right)\left(\frac{T_{\rm sw}}{2}-T_{\delta}\right)+\frac{C^3}{3(C-A)}T_{\delta}\right)}$ | $\left(\frac{1}{T_{\rm sw}}\right) \left(\frac{-\left(C+B\right)}{2} \left(\frac{T_{\rm sw}}{2}-T_{\delta}\right)+\frac{C^2}{2\left(A-C\right)} T_{\delta}\right)$ |

| D <sub>6-8</sub> | $\sqrt{\left(\frac{1}{T_{\rm sw}}\right)\left(\left(\frac{(D-A)^2}{3}+AD\right)\left(\frac{T_{\rm sw}}{2}-T_{\delta}\right)+\frac{D^3}{3(D-B)}T_{\delta}\right)}$ | $\left(\frac{1}{T_{\rm sw}}\right) \left(\frac{D+A}{2} \left(\frac{T_{\rm sw}}{2} - T_{\delta}\right) + \frac{D^2}{2 (D-B)} T_{\delta}\right)$                     |

TABLE III RMS and AVG current equations in case II a. (power transfer from HV to LV)

TABLE IV RMS and AVG current equations in case II c. (power transfer from HV to LV)

| Switch           | RMS                                                                                                                                                                                 | AVG                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|                  | $\sqrt{\left(\frac{1}{T_{\rm sw}}\right)\left(\frac{C^3}{3\left(C-B\right)}\left(\frac{T_{sw}}{2}-T_{\delta}\right)+\left(\frac{\left(A-C\right)^2}{3}+AC\right)T_{\delta}\right)}$ |                                                                                                                                               |

| $S_{6-8}$        | $\sqrt{\left(\frac{1}{T_{\rm sw}}\right)\left(\frac{D^3}{3\ (D-A)}\ \left(\frac{T_{sw}}{2}-T_{\delta}\right)+\left(\frac{(B+D)^2}{3}-B\ D\right)\ T_{\delta}\right)}$               | $\left(\frac{1}{T_{\rm sw}}\right) \left(\frac{D^2}{2 (A-D)} \left(\frac{T_{sw}}{2} - T_{\delta}\right) + \frac{-(B+D)}{2} T_{\delta}\right)$ |

| $D_{5-7}$        | $\sqrt{\left(rac{1}{T_{ m sw}} ight)rac{B^3}{3\left(B-C ight)}\left(rac{T_{sw}}{2}-T_{\delta} ight)}$                                                                            | $\left(rac{1}{T_{ m sw}} ight)  rac{B^2}{2  \left(C-B ight)}  \left(rac{T_{sw}}{2} - T_{\delta} ight)$                                     |

| D <sub>6-8</sub> | $\sqrt{\left(\frac{1}{T_{\rm sw}}\right) \frac{A^3}{3\left(A-D\right)} \left(\frac{T_{sw}}{2} - T_{\delta}\right)}$                                                                 | $\left(\frac{1}{T_{\rm sw}}\right)  \frac{A^2}{2  (A-D)}  \left(\frac{T_{sw}}{2} - T_{\delta}\right)$                                         |

TABLE V RMS and AVG current equations in case I a. (power transfer from HV to LV)

| Switch           | RMS                                                                                                                                                                                                | AVG                                                                                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S <sub>5-7</sub> | $\sqrt{\left(\frac{1}{T_{\rm sw}}\right)  \left(\frac{B^3}{3  (B-C)}  \left(\frac{T_{sw}}{2} - T_{\delta}\right) + \frac{A^3}{3  (A-C)}  T_{\delta}\right)}$                                       | $\left  \left(\frac{1}{T_{\rm sw}}\right) \left(\frac{B^2}{2 (B-C)} \left(\frac{T_{sw}}{2} - T_{\delta}\right) + \frac{A^2}{2 (A-C)} T_{\delta}\right) \right $        |

| $S_{6-8}$        | 0                                                                                                                                                                                                  | 0                                                                                                                                                                      |

| $D_{5-7}$        |                                                                                                                                                                                                    | $\left(\frac{1}{T_{\rm sw}}\right) \left(\frac{C^2}{2 \left(B-C\right)} \left(\frac{T_{sw}}{2} - T_{\delta}\right) + \frac{C^2}{2 \left(A-C\right)} T_{\delta}\right)$ |

| D <sub>6-8</sub> | $\sqrt{\left(\frac{1}{T_{\rm sw}}\right)\left(\left(\frac{\left(D-A\right)^2}{3}+DA\right)\left(\frac{T_{sw}}{2}-T_{\delta}\right)+\left(\frac{\left(B-D\right)^2}{3}+BD\right)T_{\delta}\right)}$ | $\left(\frac{1}{T_{\rm sw}}\right) \left(\frac{(A+D)}{2} \left(\frac{T_{sw}}{2} - T_{\delta}\right) + \frac{(B+D)}{2} T_{\delta}\right)$                               |

TABLE VI RMS and AVG current equations in case I b. (power transfer from HV to LV)  $\,$

| Switch           | RMS                                                                                                                                                                                                    | AVG                                                                                                                                                                |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $S_{5-7}$        | $\sqrt{\left(\frac{1}{T_{\rm sw}}\right) \cdot \frac{B^3}{3 \cdot (B-C)} \cdot \left(\frac{T_{sw}}{2} - T_{\delta}\right)}$                                                                            | $\left(\frac{1}{T_{\rm sw}}\right) \cdot \frac{B^2}{2 \cdot (B-C)} \cdot \left(\frac{T_{sw}}{2} - T_{\delta}\right)$                                               |

| $S_{6-8}$        | $\sqrt{\left(\frac{1}{T_{\rm sw}}\right) \cdot \frac{A^3}{3 \cdot (A-D)} \cdot \left(\frac{T_{sw}}{2} - T_{\delta}\right)}$                                                                            | $\left(\frac{1}{T_{\rm sw}}\right) \cdot \frac{A^2}{2 \cdot (D-A)} \cdot \left(\frac{T_{sw}}{2} - T_{\delta}\right)$                                               |

| $D_{5-7}$        | $\sqrt{\left(\frac{1}{T_{\rm sw}}\right) \cdot \left(\frac{C^3}{3 \cdot (C-B)} \cdot \left(\frac{T_{sw}}{2} - T_{\delta}\right) + \left(\frac{(A-C)^2}{3} + A \cdot C\right) \cdot T_{\delta}\right)}$ | $\left(\frac{1}{T_{\rm sw}}\right) \cdot \left(\frac{C^2}{2 \cdot (B-C)} \cdot \left(\frac{T_{sw}}{2} - T_{\delta}\right) - \frac{A+C}{2} \cdot T_{\delta}\right)$ |

| D <sub>6-8</sub> | $\sqrt{\left(\frac{1}{T_{\rm sw}}\right) \cdot \left(\frac{D^3}{3 \cdot (D-A)} \cdot \left(\frac{T_{sw}}{2} - T_{\delta}\right) + \left(\frac{(B-D)^2}{3} + B \cdot D\right) \cdot T_{\delta}\right)}$ | $\left(\frac{1}{T_{\rm sw}}\right) \cdot \left(\frac{D^2}{2 \cdot (D-A)} \cdot \left(\frac{T_{sw}}{2} - T_{\delta}\right) + \frac{D+B}{2} \cdot T_{\delta}\right)$ |

Then, the equations gathered in this work aid in the determination of the current stress in the LV side power devices of ABAC in both forward and backward operating modes considering all the hard switching and zero-voltage-switching cases.

#### REFERENCES

- G. Buticchi, S. Bozhko, M. Liserre, P. Wheeler, K. Al-Haddad, "Onboard Microgrids for the More Electric Aircraft - Technology Review", *IEEE Transactions on Industrial Electronics*, Vol. 66, No. 7, pp. 5588-5599, July 2019.

- [2] M. Kheraluwala, R. Gascoigne, D. Divan, E. Baumann, "Performance characterization of a high-power dual active bridge dc-to-dc converter",

*IEEE Transactions on Industry Applications*, Vol. 28, No. 6, pp. 1294-1301, November-December 1992.

- [3] A. Garcia-Bediaga, I. Villar, A. Rujas, L. Mir, "DAB modulation schema with extended ZVS region for applications with wide input/output voltage", *IET Power Electronics*, Vol. 11, No. 13, pp. 1755-4535, November 2018.

- [4] R. A. Mastromauro, M. C. Poliseno, S. Pugliese, F. Cupertino, S. Stasi, "SiC MOSFET Dual Active Bridge Converter for Harsh Environment Applications in a More-Electric-Aircraft", in *International Conference* on Electrical Systems for Aircraft, Railway, Ship Propulsion and Road Vehicles (ESARS), March 3-5, Aachen, Germany, 2015.

- [5] L. Tarisciotti, A. Costabeber, L. Chen, A Walker, M. Galea, "Evaluation of isolated DC/DC converter topologies for future HVDC aerospace microgrids", in *IEEE Energy Conversion Congress and Exposition* (ECCE), October 1-5, Cincinnati, OH, USA, 2017.

- [6] L. Tarisciotti, A. Costabeber, L. Chen, A Walker, M. Galea, "Current-

fed Isolated DC/DC Converter for Future Aerospace Microgrids", *IEEE Transactions on Industry Applications*, Vol. 55, No. 3, May-June, 2019.

- [7] A. Ojeda-Rodríguez, P. González-Vizuete, J. Bernal-Méndez, M. A. Martín-Prats, "A Survey on Bidirectional DC/DC Power Converter Topologies for the Future Hybrid and All Electric Aircrafts", *Energies*, 2020, 13, 4883.

- [8] L. Chen, L. Tarisciotti, A. Costabeber, P. Zanchetta, P. Wheeler, "Advanced modulation for the Active-Bridge-Active-Clamp (ABAC) Converter", in *IEEE Southern Power Electronics Conference (SPEC)*, December 4-7, Puerto Varas, Chile, 2017.

- [9] L. Chen, L. Tarisciotti, A. Costabeber, F. Gao, P. Wheeler, P. Zanchetta, "Advanced Modulations for a Current-Fed Isolated DC-DC Converter With Wide-Voltage-Operating Ranges", *IEEE Journal of Emerging and Selected Topics in Power Electronics*, Vol. 7, No. 4, pp. 2540-2552, December, 2019.

- [10] L. Chen, L. Tarisciotti, A. Costabeber, P. Zanchetta, P. Wheeler, "Parameters Mismatch Analysis for the Active-Bridge-Active-Clamp (ABAC) Converter", in *IEEE Southern Power Electronics Conference (SPEC)*, December 4-7, Puerto Varas, Chile, 2017.

- [11] A. Fernandez-Hernandez, A. Garcia-Bediaga, I. Villar, G. Abad, "Analytical Equations of the Currents in Dual Active Bridge Converter for More Electric Aircraft", in *Vehicular Power and Propulsion Conference* (VPPC), 2020.