# Ph. D Thesis

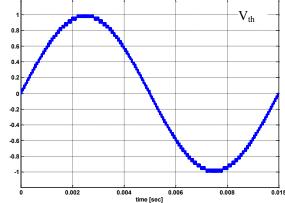

Modular Multilevel Converter based HVDC Transmission System for Offshore Wind Farms

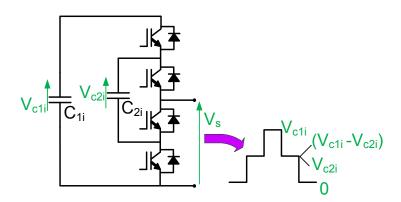

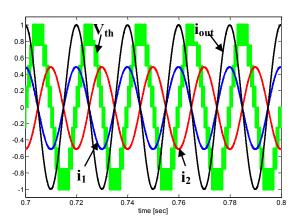

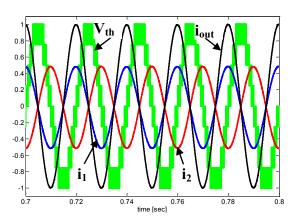

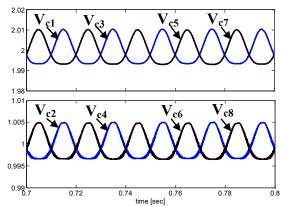

#### ESTÍBALIZ SOLAS MARTÍNEZ

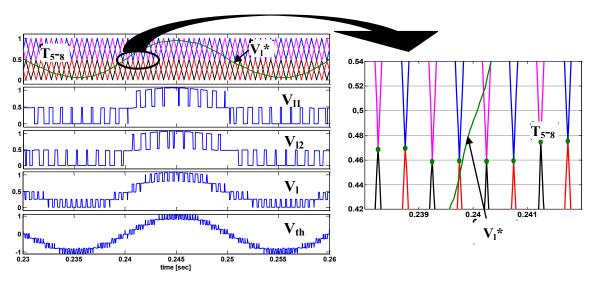

Thesis supervisors:

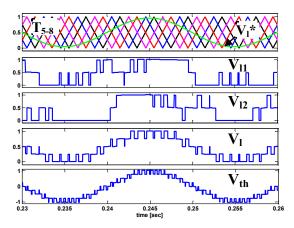

GONZALO ABAD BIAIN JON ANDONI BARRENA BRUÑA

MONDRAGÓN

**10<sup>th</sup> of July 2012**

# Acknowledgments

The work presented in this thesis was carried out in the Power Electronics Department at the Faculty of Engineering of the University of Mondragon (Spain) in cooperation with Ingeteam Corporation S.A..

My deepest gratitude goes to my supervisors Gonzalo Abad and Jon Andoni Barrena without whom none of this would have ever happened. Their professional supervision, guidance, patience and valuable time provided great help to the development of this thesis.

Some parts of this work were carried out in the Department of Electrical Engineering of the Institute of Control & Industrial Electronics at Warsaw University of Technology (Poland). It is an honour and a pleasure for me to have worked with Prof. Marian P. Kazmierkowski and his team. I would particularly want to thank Szymon, Radek, Michał, Kriss and Gosia for their hospitality and for making my stay in Warsaw such an interesting and unforgettable experience.

I am also very grateful to Ludwik Zając for his help with the implementation and startup of the laboratory test bench.

I wish to express my sincere appreciation to my colleagues from Garaia Department I came across during the four years of my PhD: Alain, Laka, Argiñe, Josu, Mazu, Manex, Baraia, Aritz, Iosu, Unai, Unaitxo, Endika, Urtzi, Egea, Patxi, Maialen, Aitziber, David, Markel, Ander, Jon, Gaizka A., Gaizka U. and those I might have forgotten for the amusing coffee breaks, lunch time and leisure.

I cannot forget to thank my friends Raúl, Anne and Julen for the funny experiences in the car journeys. Also to my basketball team mates and friends from Vitoria for such a good times together.

Finally, I would like to thank my family for their love and support during my student life. Especially to Juan, who has always been close to me.

## **Abstract**

This doctoral thesis falls within the scope of electronic power converters oriented to high voltage transmission applications, in particular the power generated in remote offshore wind farms by means of HVDC subsea cables.

This research is focused on the Modular Multilevel Converter (MMC) with two level submodules but also with multilevel topology submodules such as 3L-FC (three level flying capacitors) and 3L-NPC (three level neutral point capacitors). The main contribution of this thesis is the developed PWM based modulation strategy which allows the balancing of the total amount of submodules capacitors. It is applicable to the aforementioned submodule topologies under different working conditions as evidenced by experimental results.

# **Contents**

| 1 | Intro          | duction                                                   | 1  |

|---|----------------|-----------------------------------------------------------|----|

|   | 1.1 Wi         | nd energy generation overview                             | 2  |

|   | 1.1.1          | Wind power installations                                  | 2  |

|   | 1.1.2          | Offshore wind power generation                            | 3  |

|   | 1.1.3          | General wind farm layout                                  | 5  |

|   | 1.2 Des        | scription of a HVDC transmission based offshore wind farm | 9  |

|   | 1.2.1          | Wind farm                                                 |    |

|   | 1.2.2          | Wind turbines                                             |    |

|   | 1.2.3          | Local inter-turbine grid                                  |    |

|   | 1.2.4          | Offshore platform transformer                             |    |

|   | 1.2.5          | Converters                                                |    |

|   | 1.2.6          | HVDC transmission cables                                  | 14 |

|   | 1.2.7          | Resonant passive filters                                  | 16 |

|   | 1.2.8          | Electrical grid                                           | 18 |

|   | 1.2.9          | Coordinated control system                                | 18 |

|   | 1.3 Con        | nverter technologies                                      | 20 |

|   |                | DC-VSC topologies                                         |    |

|   |                |                                                           |    |

|   | 1.4.1          | Two level converter                                       |    |

|   | 1.4.2          |                                                           |    |

|   | 1.5 Pur        | pose of the thesis                                        | 28 |

|   | 1.6 Des        | scription of the chapters                                 | 28 |

| 2 | Mod            | ular Multilevel Converter (MMC)                           | 30 |

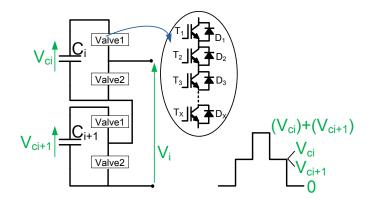

|   | 2.1 MN         | AC with 2L submodules                                     | 32 |

|   |                |                                                           |    |

|   | 2.1.1          | Modelling                                                 |    |

|   | 2.1.2<br>2.1.3 | Modulation                                                |    |

|   |                |                                                           |    |

|   | 2.2 MN         | AC with 3L-FC submodules                                  |    |

|   | 2.2.1          | Modelling                                                 |    |

|   | 2.2.2          | Modulation                                                |    |

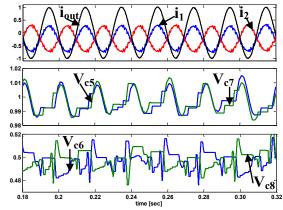

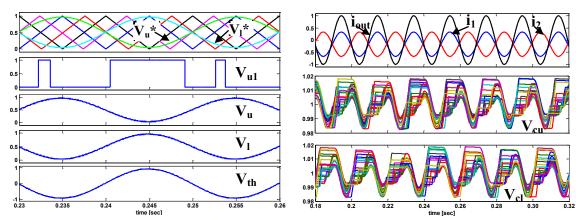

|   | 2.2.3          | Simulation results                                        | 47 |

|   | 2.3 MN         | AC with 3L-NPC submodules                                 |    |

|   | 2.3.1          | Modelling                                                 |    |

|   | 2.3.2          | Modulation                                                |    |

|   | 2.3.3          | Simulation results                                        | 54 |

|   | 2.4 Siz        | ing of the passive elements of the MMC                    | 55 |

|   | 2.4.1          | Sizing of the capacitors                                  |    |

|   | 2.4.2          | Sizing of the inductances                                 |    |

|   | 2.4.3          | Summary of passive elements                               | 62 |

|   | 2.5 Con        | ntrol of the voltage of the submodules                    | 63 |

|    |      | .5.1 Capacitors voltage control                          |                   |           |     |

|----|------|----------------------------------------------------------|-------------------|-----------|-----|

|    | 2.6  | Unbalances of the submodule voltages .                   |                   |           | 66  |

|    | 2.7  | Conclusions                                              |                   |           | 68  |

| _  |      |                                                          |                   |           |     |

| 3  |      | Modulation algorithm with capac                          | •                 | _         |     |

| su | ıbmo | odules                                                   |                   |           | 69  |

|    | 3.1  | Description of the Modulation Algorithm                  | m applied to 2L s | ubmodules | 71  |

|    | 3.2  | Modulation applied to 3L-FC submodul                     | es                |           | 75  |

|    | 3.3  | Modulation applied to 3L-NPC submod                      | ules              |           | 77  |

|    | 3.3  | .3.1 Modification in the modulation of the MMC           |                   |           |     |

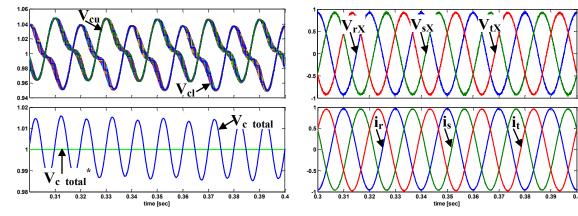

|    | 3.4  | Validation of the modulation for a HVD                   | C application     |           | 81  |

|    | 3.5  | Conclusions                                              |                   |           | 86  |

| 4  | Е    | Experimental validation of the mod                       | ulation strateg   | V         | 88  |

|    | 4.1  | Description of the laboratory test bench                 | 0.                | •         |     |

|    |      |                                                          |                   |           |     |

|    | 4.2  | Implementation of the control system or                  | ı a dSPACE        |           | 90  |

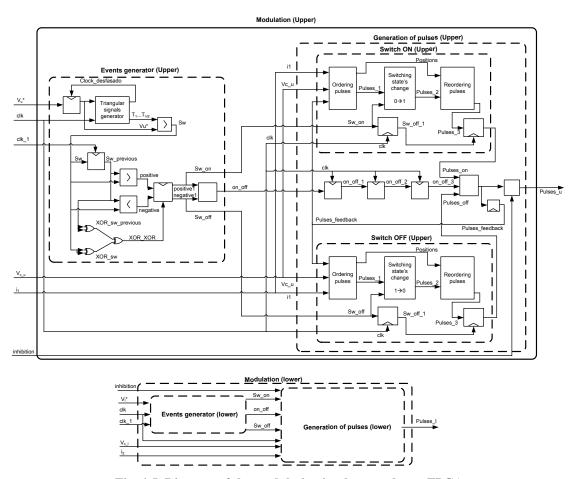

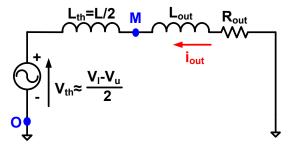

|    | 4.3  | Implementation of the modulation on a                    | FPGA              |           | 92  |

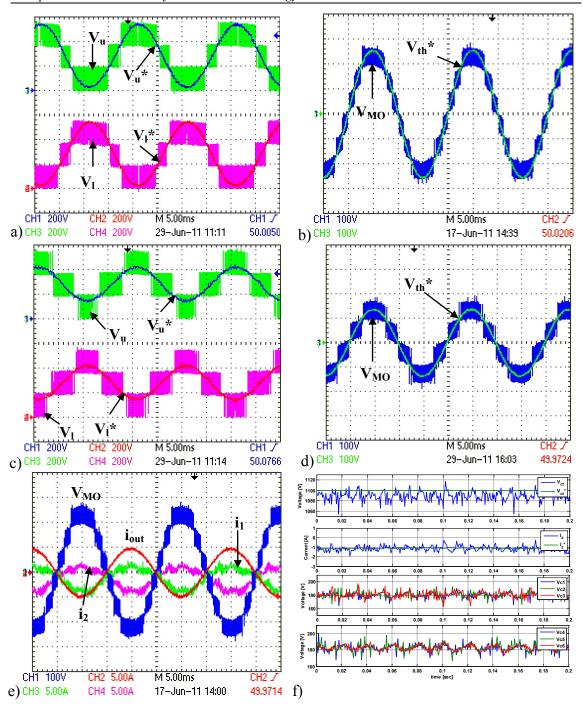

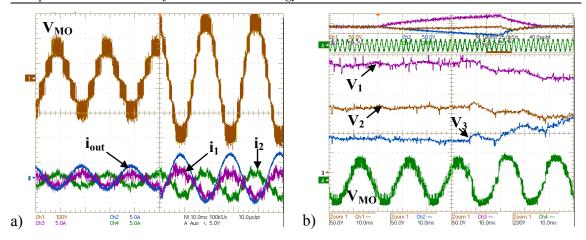

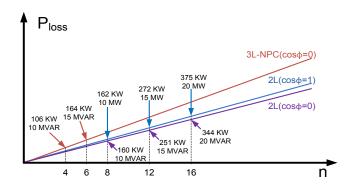

|    | 4.4  | Experimental Results                                     |                   |           |     |

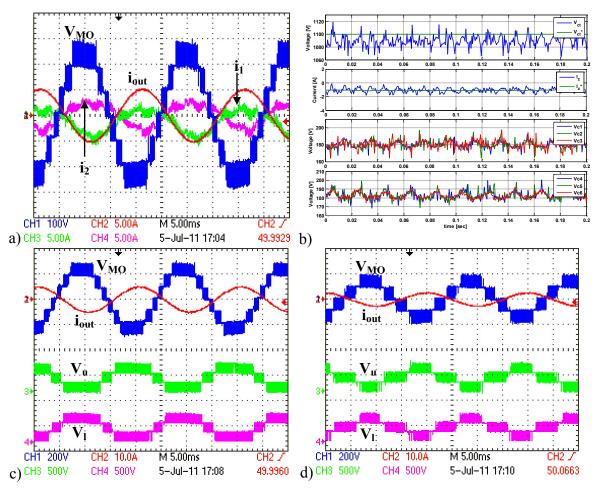

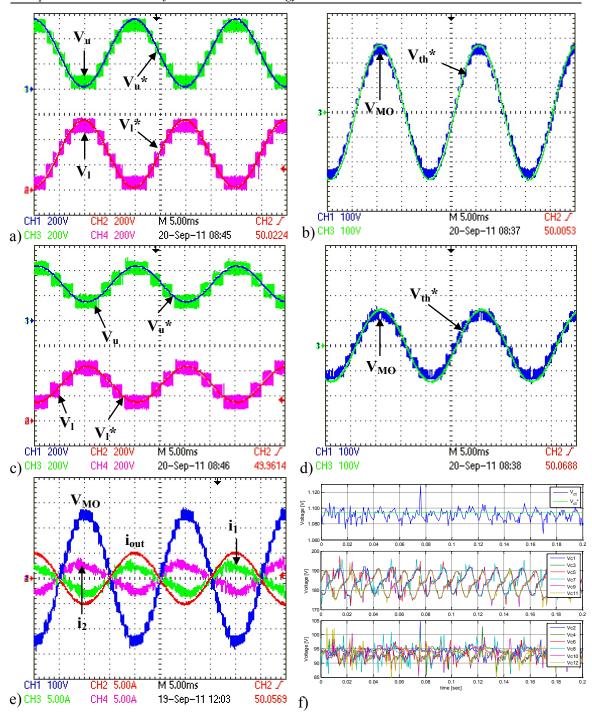

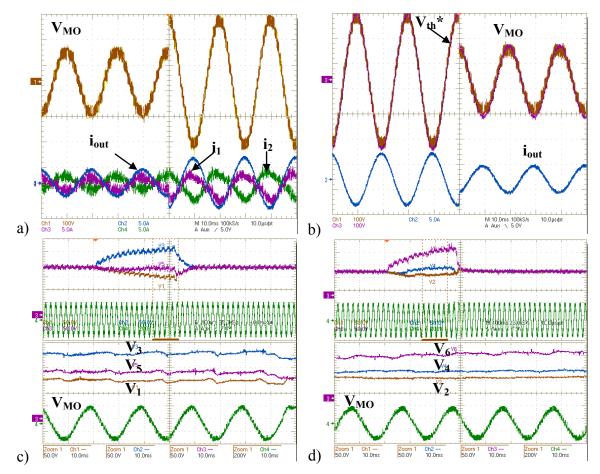

|    |      | .4.1 Results with 2L submodules                          |                   |           |     |

|    |      |                                                          |                   |           |     |

|    | 4.5  | Conclusions                                              |                   |           | 101 |

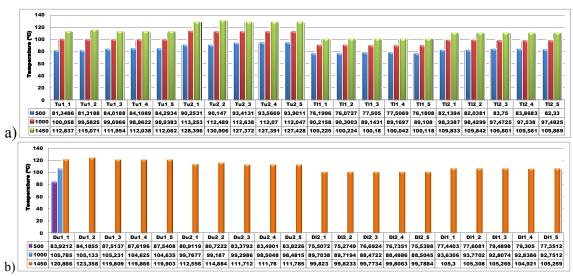

| 5  | A    | Analysis of MMC with different sul                       | bmodules          |           | 102 |

|    | 5.1  | Output voltage analysis of MMC topolo                    | gy                |           | 103 |

|    | 5.   | .1.1 MMC topology with different submodule co            | oncepts           |           | 104 |

|    | 5.   | .1.2 Output voltage quality analysis                     |                   |           | 106 |

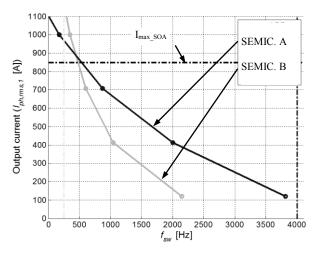

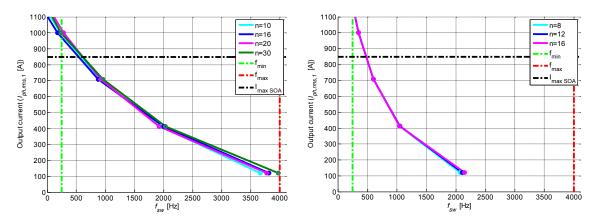

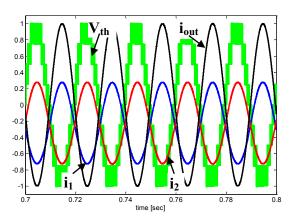

|    | 5.2  | Output current capacity analysis of MM                   | C topology        |           | 109 |

|    | 5.2  | .2.1 Semiconductors                                      |                   |           | 111 |

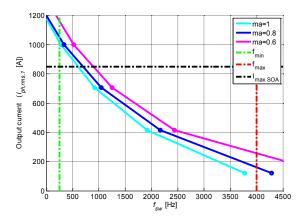

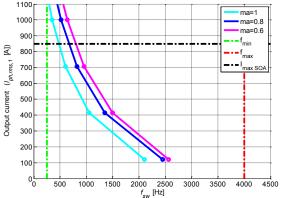

|    | 5.2  | .2.2 Output current analysis at different modulat        | ion indexes       |           | 113 |

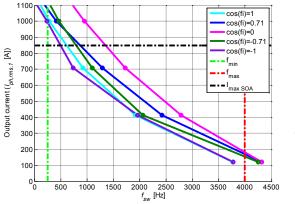

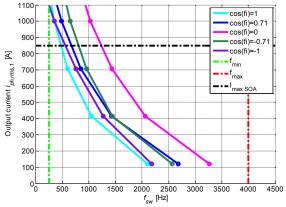

|    | 5.2  | .2.3 Output current analysis at different $cos(\varphi)$ |                   |           | 114 |

|    | 5.2  | .2.4 Output current analysis with different numb         | er of submodules  |           | 115 |

|    | 5.2  | .2.5 Output current analysis with serialized subn        | nodule concept    |           | 117 |

|    | 5.2  | .2.6 Output current analysis with 3L-FC submod           | lule concept      |           | 118 |

|    | 5.2  | .2.7 Output current analysis with 3L-NPC subm            | odule concept     |           | 118 |

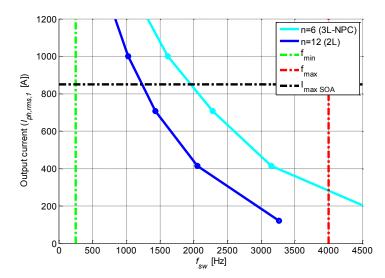

|    | 5.2  | .2.8 Extrapolation of the power losses                   |                   |           | 120 |

|    | 5.2  | .2.9 Analysis of the submodules capacitors               |                   |           | 120 |

|    | 5.2  | .2.10 Extrapolating to a HVDC application                |                   |           |     |

|    | 5.2  | .2.11 Final comparison                                   |                   |           | 127 |

|    | 5.3  | Conclusions                                              |                   |           | 130 |

| 6  | Problems associated with disturbances and feasible solutions |      |                                                   |     |  |  |  |

|----|--------------------------------------------------------------|------|---------------------------------------------------|-----|--|--|--|

|    | 6.1                                                          | Spe  | ecific characteristics of the MMC working as HVDC | 134 |  |  |  |

|    | 6.                                                           | 1.1  | Precharge of the capacitors                       | 134 |  |  |  |

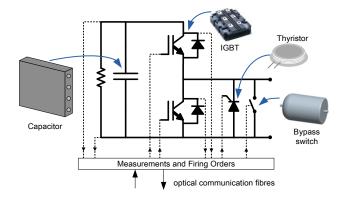

|    | 6.                                                           | 1.2  | Control hardware                                  | 137 |  |  |  |

|    | 6.                                                           | 1.3  | Voltage supply for the drive of the submodule     | 137 |  |  |  |

|    | 6.                                                           | 1.4  | Submodules and converter arrangements             | 138 |  |  |  |

|    | 6.                                                           | 1.5  | Onshore and offshore substations                  | 139 |  |  |  |

|    | 6.2                                                          | Pro  | blems associated with failures                    | 140 |  |  |  |

|    | 6.                                                           | 2.1  | AC current interrupter                            | 140 |  |  |  |

|    | 6.                                                           | 2.2  | Overvoltage and overcurrent protections           | 141 |  |  |  |

|    | 6.                                                           | 2.3  | DC side pole to pole fault                        | 142 |  |  |  |

|    | 6.                                                           | 2.4  | Grid faults                                       | 144 |  |  |  |

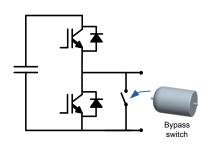

| 6  |                                                              | 2.5  | Failure management in submodules                  | 147 |  |  |  |

|    | 6.3                                                          | Coı  | nclusions                                         | 154 |  |  |  |

| 7  | C                                                            | Conc | lusions and future work                           | 156 |  |  |  |

|    | 7.1                                                          | Coı  | nclusions                                         | 156 |  |  |  |

|    | 7.2                                                          | Coı  | ntributions                                       | 157 |  |  |  |

|    | 7.3 Future work                                              |      |                                                   |     |  |  |  |

| Ρι | ıblic                                                        | atio | ns                                                | 160 |  |  |  |

| В  | iblio                                                        | grap | ohy                                               | 161 |  |  |  |

| A  | pper                                                         | ndix |                                                   | 169 |  |  |  |

## List of abreviations

AC Alternative Current

APO Alternative Phase Opposition

CTL Cascaded Two Level

DC Direct Current

HVDC High Voltage Direct Current

FC Flying Capacitor

FRT Fault Ride Through

IGBT Insulated Gate Bipolar Transistor

IGCT Integrated Gate-Commutated Thyristor

LCC Line Commutated Converters

LSPWM Level Shifted Pulse Width Modulation

LV Low Voltage

LVRT Low Voltage Ride Through

MMC Modular Multilevel Converter

MPC Multi Point Clamped MV Medium Voltage

HVAC High Voltage AC Transmission

MTDC Multi-terminal DC

MVAC Medium Voltage AC Transmission

NPC Neutral Point Clamped NPP Neutral Point Piloted

PC Collector Point

PCC Point of Common Coupling

PEBB Power Electronics Building Block

PF Power Factor

PH Phase

PO Phase Opposition

PSPWM Phase Shifted Pulse Width Modulation

PWM Pulse Width Modulation

SF<sup>6</sup> Sulfurhexaflouride

SHE Selective Harmonic Elimination STATCOM Static Synchronous Compensator

SVM Space Vector Modulation

THD Total harmonic Distortion

VSC Voltage Source Converter

WPP Wind Power Plant

XLPE Cross Linked Polyethylene

ZnO Zinc Oxide

# Chapter 1

# Introduction

In recent years, the continuously increasing demand for electric power is becoming our society more involved in saving energy. Climate change concerns together with high oil prices and increasing government support, have drived the use of renewable energy with the aim of dramatically reducing the emissions of greenhouse gases that harm the environment.

The naturally replenished wind energy resource has undergone a spectacular growth over the last years. Due to this fast increase, the most suitable sites to build an onshore wind farm are already in use, so offshore wind power is destined to have an important role. The evolution of the wind farms from onshore to offshore has led to some technological challenges, such as the energy transmission system or energy integration in the main grid. The economic access to remote renewable energy sources requires an electric energy transmission system that bridges very long distances with low losses. This is why the interest in High Voltage Direct Current (HVDC) technology has been revived.

The main advantage the HVDC offers versus High Voltage Alternative Current (HVAC) for bulky and long-distance electrical underwater power transmission is that HVDC avoids the heavy currents required by the cable capacitance improving the capacity of transmitting active power. For shorter distances, the higher cost of DC conversion equipment compared to an AC system may still be warranted, due to other benefits of direct current links.

# 1.1 Wind energy generation overview

#### 1.1.1 Wind power installations

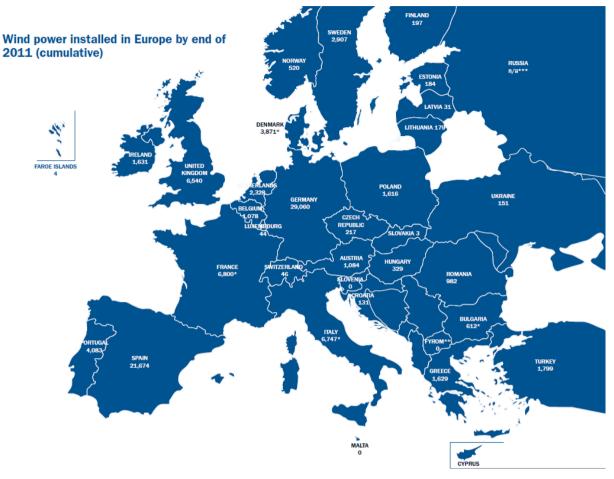

Fig. 1-1. Cumulative wind power installed in Europe by the end of 2011. Source: EWEA [1].

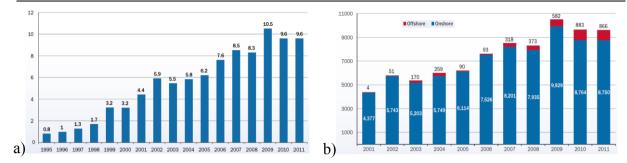

As described in [1], since 1995 wind energy has played an increasing and accelerating role in the evolution of the power sector. Despite the fact that most of the 94 GW of wind energy installed in the EU by the end of 2011 were added in the last 10 years, annual wind power installations in the EU have increased steadily over the past 17 years from 814 MW in 1996 to 9616 MW in 2011, an average annual growth rate of 15.6% (the progression is exposed in Fig. 1-2a). From those 9616 MW installed throughout 2011, 866 MW are offshore wind's share which represents a 9% of total installations, a little less than in 2010 (9.2%) as shown in Fig. 1-2b. Germany remains the EU country with the largest installed capacity (29 GW), followed by Spain (21.7 GW), Italy (6.7 GW), France (6.8 GW) and the UK (6.5 GW). Nine other countries have over 1 GW of installed capacity: Portugal, Denmark, the Netherlands, Sweden, Ireland, Greece, Poland, Austria and Belgium.

Fig. 1-2. a) Annual wind power installations in EU in GW. b) Annual onshore and offshore installations in MW. Source: EWEA [1].

This significant deployment of wind energy has been instrumental in reducing greenhouse gas emissions from the power sector, with more wind power capacity being installed in the EU than any other power generating technology in the last 10 years, except for gas. The 21st century sees the EU power sector moving away from fuel oil, coal and nuclear while continuing to increase its total installed capacity with gas, wind and solar PV to meet increasing demand.

#### 1.1.2 Offshore wind power generation

Based on information available at [2], the average size of offshore turbines grid connected during 2011 was 3.6 MW. Since 2000, when the first 2 MW turbines were introduced, the average size of offshore turbines has been increasing, albeit not linearly, and in the middle of the last decade turbines in the 3+ MW range were being deployed. The first 5 MW turbines were used in 2007 at Beatrice in the UK and 2008 at Hooksiel in Germany. This size turbine became more common and, by 2011 the average size of offshore turbines was 3.6 MW, 20% more than in 2010 (3 MW) and over 6 times more than the turbines used in the early nineties (Fig. 1-3a). Moreover, in 2011 REpower installed the first turbines with a rated capacity above 5 MW at Ormonde in the UK. Looking at the under construction offshore wind farm pipeline (4,583 MW), the Siemens 3.6 MW turbine will continue to be used extensively. However, roll-out of 5 – 6 MW turbines means that the under construction pipeline averages 3.9 MW.

Owing to the incessant development of wind turbines, the average size of offshore wind farms has been increasing steadily (Fig. 1-3b). A total of 1371 offshore turbines are now installed and grid connected in European waters totalling 3812.6 MW spread across 53 wind farms in 10 countries. In 2011, the average size of the projects, once fully completed, is just under 200 MW, 45 MW (+29%) more than in 2010 when Thanet, a 300 MW project in the UK, was the largest offshore wind farm completed and fully grid connected in the world.

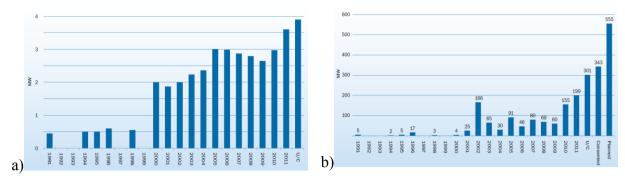

Fig. 1-3. a) Average annual size of offshore wind turbines in MW. b) Average wind farm size in MW. Source: EWEA [2].

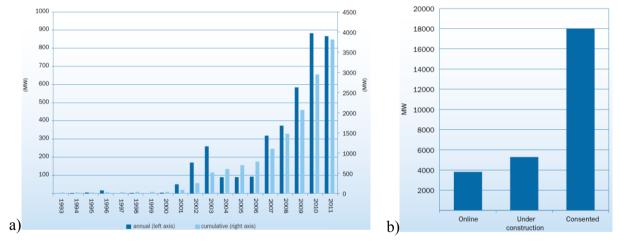

This trend is expected to continue and, indeed, accelerate as the average size of offshore wind farms currently under construction is almost 300 MW, thanks to the construction that has already started on the first phase of the London Array project which will be 630 MW (the progression of the last years appears in Fig. 1-4a). As the technology matures and it is expected that wind farms will continue to grow in size, the average size of projects being planned by developers increases to 555 MW.

Fig. 1-4. a) Cumulative and annual offshore wind installations in MW. b) Offshore wind farms online, under construction and consented in MW. Source: EWEA [2].

The 9 offshore projects under construction in 2011, will bring online a further 2375 MW of capacity. These projects alone will bring total installed capacity in Europe to 6188 MW, a 62% increase. Furthermore, preparatory work on nine other projects started in 2011. These projects have a cumulative capacity of 2910 MW, 2272 in Germany and 638 in the UK. Therefore, when these 18 projects are completed, total installed offshore wind capacity in Europe would reach 9 GW. Furthermore, EWEA has identified 18 GW of fully consented projects in 12 European countries (information represented in Fig. 1-4b).

The UK is by far the largest market with 2094 MW installed, representing over half of all installed offshore wind capacity in Europe. Denmark follows with 857 MW (23%), then the Netherlands (247 MW, 6%), Germany (200 MW, 5%), Belgium (195, 5%), Sweden (164, 4%), Finland (26 MW in near-shore projects) and Ireland 25 MW. Norway and Portugal both have a full-scale floating turbine (2.3 MW and 2 MW respectively).

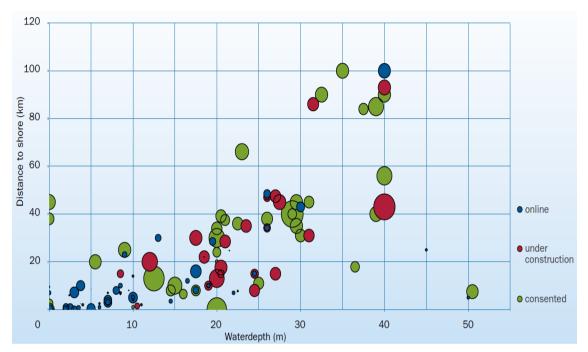

Fig. 1-5. Average size, distance to shore and water depth. Source: EWEA [2].

As far as the location of offshore wind farms is concerned, they are increasingly being built further from the coast and in deeper waters. Analysis of the planned projects pipeline shows that this trend will continue. In 2011 average water depth of wind farms was 22.8 m and average distance to shore 23.4 km. In Fig. 1-5 can be observed that there is already online a wind farm 100 km far away from the coast where the water depth is 40 meters, and similar distances as well as depth are chosen for future constructions. This is why for projects under construction, average depth is 25.3 m and distance to shore 33.2 km.

#### 1.1.3 General wind farm layout

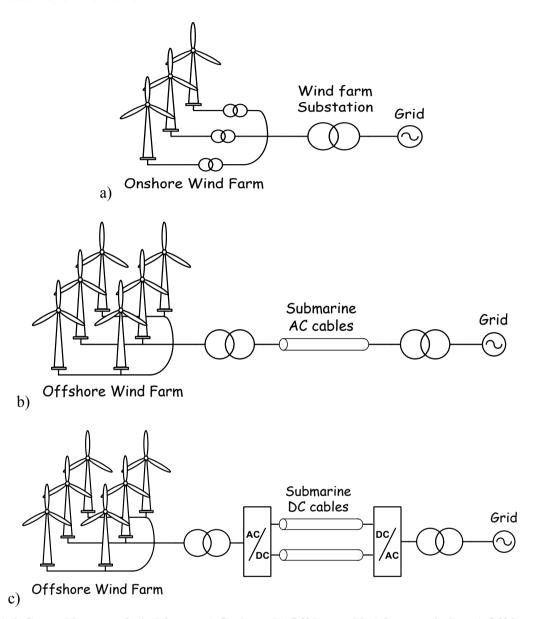

An evaluation of various large-scale wind farms layout are investigated in [3] but mainly three of them can be found all over the world as represented in Fig. 1-6: onshore, offshore with AC transmission and offshore with HVDC transmission to shore.

Onshore turbine installations are placed in hilly or mountainous regions. The exact position of the turbines is carefully chosen: these tend to be on ridgelines generally at least three kilometres inland from the nearest shoreline to exploit the topographic acceleration as the wind accelerates over a ridge. The additional wind speeds gained in this way can increase energy produced because more wind goes through the turbines. Many of the largest operational onshore wind farms are located in the USA but as listed in Table 1-1 they are installed all over the world

Fig. 1-6. General layouts of wind farms: a) Onshore. b) Offshore with AC transmission. c) Offshore with HVDC transmission.

The electricity generated in the wind turbines is typically low voltage. As the inter-turbine grid is usually medium voltage, a transformer is required at the output of each turbine to step up its voltage level. All the energy collected on the wind farm is again transformed at the substation to high voltage for the bulk transfer of the electrical energy, from the collecting point to electrical substations located near demand centres. The main function of the transformer is, besides voltage level conditioning, galvanic insulation of the two connected circuits.

| Wind farm           | Current Capacity | Country   | No. of turbines | Production date |

|---------------------|------------------|-----------|-----------------|-----------------|

| Roscoe              | 781.5 MW         | USA       | 627             | 2009            |

| <b>Horse Hollow</b> | 735.5 MW         | USA       | 421             | 2006            |

| Dabancheng          | 500 MW           | China     | 300             | 2009            |

| Fântânele-Cogealac  | 387.5 MW         | Romania   | 240             | 2011            |

| Whitelee            | 322 MW           | Scotland  | 140             | 2009            |

| Lake Bonney         | 279 MW           | Australia | 99              | 2008            |

Table 1-1. Some operational onshore wind farms.

Unlike onshore wind farms, offshore ones refer to the construction of extensive wind farms in open bodies of water. Better wind speeds are available off the coast compared to on land, because it is typically more consistent and stronger over the sea, due to the absence of topographic features that disrupt wind flow. So its contribution in terms of electricity supplied is higher. Furthermore, offshore wind turbines are less obtrusive than turbines on land, as their apparent size and noise is mitigated by distance.

There are nonetheless trade-offs. The operation and maintenance are more complicated than in land, the environment is more corrosive owing the salinity and humidity, the construction of the foundations on the seabed difficulties and increases the installation costs. However, the main differentiating feature is the energy transmission system to the shore.

Two transmission options are used to transport the energy generated on the offshore wind farms to the grid connection point on the shore: HVAC or HVDC. Both the generation and the distribution grid are AC, so by using HVAC submarine cables only some transformers to step up and accommodate the voltage are required at both transmission ends in order to reduce the resistive line losses. On the other hand, if DC is the transmission choice, besides the transformers an apparatus to convert from AC to DC and vice versa is imperative as represented in Fig. 1-6c. The latter requirement is an important drawback which can be countered with the power savings related to reactive currents. Due to the short distance between the conductor and the shield, subsea power cables exhibit a much higher shunt capacitance, in the order of 100-200 nF/km meanwhile in overhead lines it is around 9-13 nF/km. Accordingly, a large charging current flows through the cable as soon as it is energized. This current is proportional to the length of the cable an even at moderate lengths (50-150 km) its magnitude can approach the cable's rated current reducing the power transfer capability of the cable [4]. AC power transmission suffers from these reactive losses meanwhile the only losses in a DC (zero frequency) transmission line are the resistive ones, which are present in AC lines as well.

On the last years several studies ([5], [6], [7] for instance) have been conducted in this field trying to determine the most cost-effective alternative. Although the optimum layout

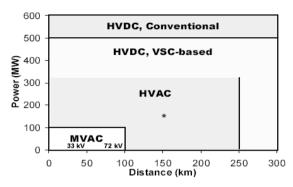

depending on rated power and distance to shore is not clear, all the analysis concur in stating that HVDC is the most attractive for high power and long distances. An example is shown in Fig. 1-7 in which HVDC is recommended for power higher than 300 MW or a submarine transmission longer than 250 km.

Fig. 1-7. Approximate ranges for voltage options as a function of power and distance [7].

All the currently operational offshore wind farms have HVAC transmission system some of which are listed in Table 1-2 rated by the latest commissioning date. However, BorWin1 is a 400 megawatt (MW) offshore wind farm with HVDC transmission that is presently under construction and is expected to be fully operational by the end of 2012. It will be an 80-turbine wind farm, located 100 kilometres northwest of the isle Borkum (Germany), in water which is 40 metres deep.

| Wind farm                     | <b>Total Capacity</b> | Country     | No. of turbines | Commissioning date |

|-------------------------------|-----------------------|-------------|-----------------|--------------------|

| Longyuan Rudong<br>Intertidal | 131.3 MW              | China       | 37              | 2012               |

| Ormonde                       | 150 MW                | UK          | 30              | 2012               |

| Walney (phases 1&2)           | 367.2 MW              | UK          | 102             | 2012               |

| Baltic 1                      | 48 MW                 | Germany     | 21              | 2011               |

| Thanet                        | 300 MW                | UK          | 100             | 2010               |

| Bligh Bank (Belwind)          | 165 MW                | Belgium     | 55              | 2010               |

| <b>Gunfleet Sands</b>         | 172 MW                | UK          | 48              | 2010               |

| Donghai Bridge                | 102 MW                | China       | 34              | 2010               |

| Robin Rigg (Solway Firth)     | 180 MW                | UK          | 60              | 2010               |

| Rødsand II                    | 207 MW                | Denmark     | 90              | 2010               |

| Horns Rev II                  | 209 MW                | Denmark     | 91              | 2009               |

| Alpha Ventus                  | 90 MW                 | Germany     | 12              | 2009               |

| Rhyl Flats                    | 60 MW                 | UK          | 25              | 2009               |

| Princess Amalia               | 120 MW                | Netherlands | 60              | 2008               |

| Lynn and Inner Dowsing        | 194 MW                | UK          | 54              | 2008               |

Table 1-2. Latest operational offshore wind farms.

Onshore wind farms as well as offshore wind farms with AC transmission system are a mature technology. Therefore, from the three aforementioned wind farm layouts this study will be focused in the last one, offshore wind farms with HVDC transmission system.

Fig. 1-8. Photographs of Horns Rev II offshore wind farm taken from. Source: [8].

# 1.2 Description of a HVDC transmission based offshore wind farm

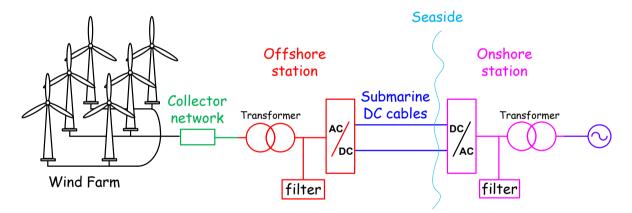

This section gives an overview of how the energy transmission from offshore wind farms to shore is accomplished. The complete layout of the system is illustrated in Fig. 1-9 and then a brief description of its main parts is presented.

Fig. 1-9. General layout of an offshore wind farm transmission system.

The electricity generated in the wind turbines, which are placed further away from the shoreline, is collected in the medium voltage inter-turbines network. In order to reduce transmission losses, at the offshore station it is transformed to high voltage, then filtered to eliminate undesirable harmonics and finally converted to DC by a power converter. Afterward it is ready for transferring by submarine cables towards the onshore station where the reverse action takes place. Once it is again converted to AC and filtered on such a way that it fulfils the grid codes, the electricity is adapted to the voltage levels of the grid on the onshore connection point.

#### 1.2.1 Wind farm

The offshore wind power plant (WPP) is considered to be a large size and capacity wind farm located at more than 100 kilometres off the coast where noise and visual impact cannot be perceived from the inhabited areas. Assuming that the wind power has a non-controllable stochastic character since it depends on the weather conditions, better wind speeds (stronger and less roughness) are available offshore than on land.

It consists of a large number of wind turbines which can be classified by three parameters according to most of the authors [9], [10]: the direction of the rotor axis (vertical or horizontal), the number of rotor blades and the rotor position (upwind or downwind). They are comprised of rotor blades, a gearbox, an electrical AC generator, the associated power electronics and measuring devices (anemometer and wind vane primarily).

Due to the large size of the wind farm, the average distance between wind turbines and the collecting point can be of some kilometres. This is why each turbine has its own transformer to step-up the output voltage level to the medium voltage of inter-turbines line with the aim of reducing losses along the mentioned distance.

#### 1.2.2 Wind turbines

Up to 2005 all turbines installed offshore had been 2 or 3 MW. Since 2006, 3.6 and 5 MW wind turbines have been introduced [11]. But the situation is changing. Experts state that we stand on the threshold of a revolution in the wind power and with the right equipment besides strategy, huge returns on investment are achievable. That is why nowadays, a new generation of turbines 100 per cent dedicated to offshore environments are being developed [12].

As a progression from the G10X 4.5-MW turbine, Gamesa has developed the G11X, a 5 MW permanent magnet generator with full-scale converter [13]. Regarding Repower Systems, after the great success in REpower 5M, the new REpower 6M offshore wind turbine represents the further development of its predecessor with a 6 MW asynchronous doubly-fed generator [14]. That same rated output power has achieved Siemens Wind Power in their SWT-6.0-120 prototype in which several trials to assess its performance and availability are now being conducted. This wind turbine is fitted with an innovative direct drive and therefore does not require a gearbox. If everything proceeds according to schedule, the SWT-6.0-120 wind turbine should enter series production in 2014 [15].

In the same way, Alstom has built up a new generation, high yield offshore wind turbine prototype: Haliade 150 - 6 MW, with a direct drive permanent magnet generator plus a full conversion converter [16].

With the launch of the V164-7.0 MW Vestas introduces almost the largest wind turbine: a 7 MW permanent magnet generator provided with a full scale converter which has been designed with challenging offshore conditions in mind [12]. There is still a bigger one: Enercon E-126 which is able to generate up to 7.5 MW with a direct-drive annular generator [17].

Fig. 1-10. Wind turbine components. Source: NREL.

Fig. 1-11. A wind turbine general system design in which all its components are specified. Source: [18].

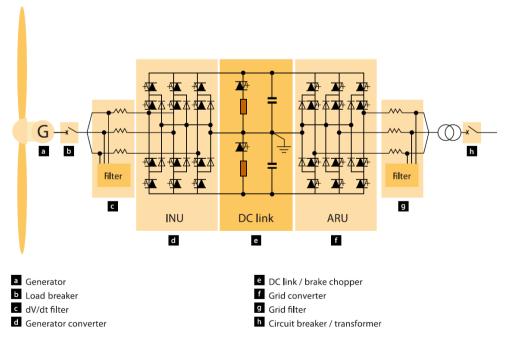

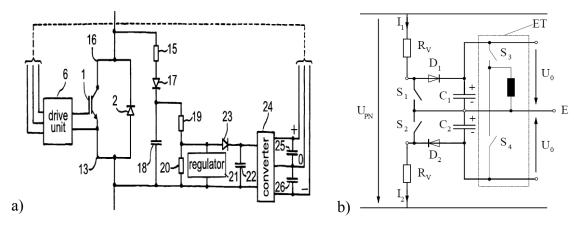

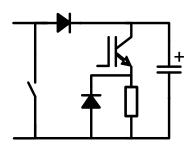

Each wind turbine has on a single platform inside the tower a compact full scale converter installed. As the power ratings of the wind turbines increases, medium voltage converters have become more competitive. The technology of the converter is in general a 3L neutral-point-clamped (see Fig. 1-11). This converter, which uses PEBB technology IGCT as semiconductor, acts as a drive and can operate in all 4 quadrants, providing bidirectional power flow and full reactive power control. Moreover, during grid disturbances, the brake chopper dissipates the generated power in a shunt resistor. As soon as the fault has cleared, the turbine is taken back smoothly onto the grid in compliance with grid codes.

#### 1.2.3 Local inter-turbine grid

The local inter-turbine grid can be AC or DC (this feature does not determinate the transmission systems technology), but the installed majority is an AC collector grid. Regarding the voltage level, the usage of above 36kV for the inter-turbine grid becomes uneconomic due to the impossibility to accommodate switchgear and transformers in each turbine tower. So, a medium voltage such as 33kV is widely used for collection schemes [19].

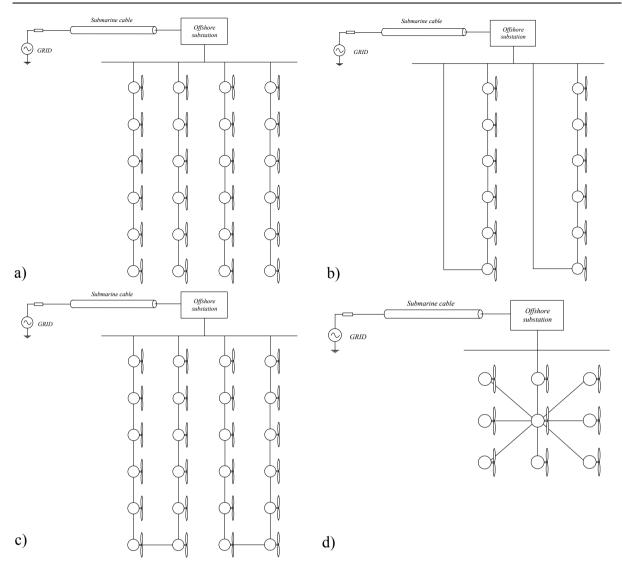

The cable length to the offshore collector point depends on the number of wind turbines, their disposition and the space among them which must be enough to avoid turbulences generated at the surrounding turbines, usually from 500 to 1000 m between two of them [20]. There are various standard arrangements for wind farm collector systems but these four designs are the most employed in existing offshore wind farms:

- Radial design

- Single side ring design

- Double-side ring design

- Star design

The layouts of the four listed designs are illustrated in Fig. 1-12 from the simplest one to the most reliable [21]. The differences are related to the length and sizing of the cable, redundancy, energy saving thanks to extra paths, etc.

Fig. 1-12. Layout of the local inter-turbine grid. a) Radial design. b) Single side ring design. c) Double side ring design. d) Star design.

#### 1.2.4 Offshore platform transformer

On the offshore transformer platform step-up transformation takes place to interconnect the VSC with the AC network. The main function of the transformers is to adapt the voltage level of the AC network to a voltage level suitable to the converter and galvanic insulation of the two connected circuits. This voltage level can be controlled using a tap changer, which will maximize the reactive power flow.

Dry type transformers are preferred in offshore applications rather than oil-filled transformer basically because they require less maintenance services as well as space. Oil-filled transformers are capable of working at higher voltages and powers thanks to its better cooling characteristics. However, this liquid needs a regular maintenance which is a handicap in

station on the sea. Moreover this type of transformers needs greater installation space owing to the fire safety measures which must be taken to avoid oil combustion.

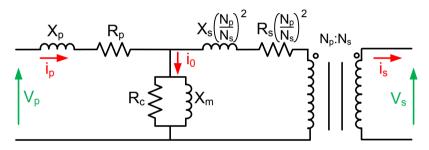

The transformer is modelled using the equivalent circuit designated in [22] as the classical approach and depicted in Fig. 1-13. Power loss in the windings is current-dependent and is represented as in-series resistances  $R_p$  and  $R_s$ . Flux leakage results in a fraction of the applied voltage dropped without contributing to the mutual coupling, and thus can be modelled as reactances of each leakage inductance  $X_p$  and  $X_s$  in series with the perfectly coupled region. Iron losses are caused mostly by hysteresis and eddy current effects in the core and are represented by a resistance  $R_c$  in parallel with the ideal transformer. A core with finite permeability requires a magnetizing current  $I_m$  to maintain the mutual flux in the core. It is modelled as a magnetizing reactance  $X_m$  in parallel with the core loss component  $R_c$ . If the secondary winding is made open-circuit, the current  $i_0$  taken by the magnetizing branch represents the transformer's no-load current.

Fig. 1-13. Transformer electrical equivalent circuit per phase with secondary impedances referred to primary side.

#### 1.2.5 Converters

The converter is the distinct and essential element of this transmission system. In total two of these are needed in the system, one at each HVDC end. An AC/DC is placed on the offshore station and the DC/AC is a part of the onshore converter station. As will be later detailed, two principal technologies exist for this purpose: LCC (Line Commutated Converter) using the classical thyristors and VSC (Voltage Source Converter) using IGBTs or IGCTs.

#### 1.2.6 HVDC transmission cables

They are the physical medium to transfer the energy from the offshore station to the onshore PCC (Point of Common Coupling). For long distance transmission of bulk electrical power generated at the wind farm to the grid, high voltage direct current cables are installed undersea. HVDC systems may be less expensive and suffer lower electrical losses in contrast

with the more common alternating current systems because it avoids the heavy currents required by the cable capacitance.

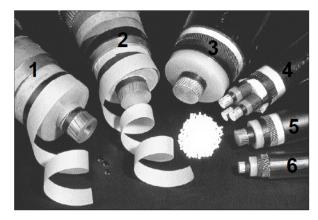

- 1. LPOF for a.c. or d.c.

- 4. Three core XLPE for a.c.

- 2. MIND for d.c.

- 5. Extruded sea cable for VSC

- 3. Single core XLPE for a.c.

- 6. Extruded land cable for VSC

Fig. 1-14. High voltage cables. Source: ABB [23].

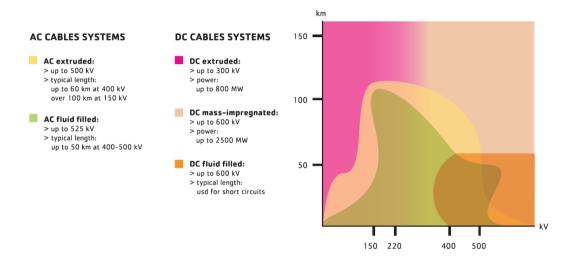

Fig. 1-15. Power transmission cable systems. Source: [24].

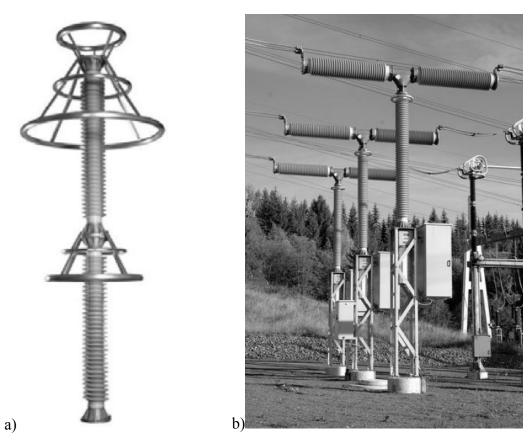

Some of the basic requirements of a submarine cable are: Long-life design, low environmental impact as well as maintenance, mechanical resistance capable of withstanding undersea installation, high reliability and long manufacturing lengths to minimize cable joints. There are different available type of cables depending on the insulation and the transmission parameters such as power and voltage. Mass Impregnated cables (high-density paper tapes impregnated with a high-viscosity compound) have proven suitable for voltage ratings up to 600kV DC and current rating up to 1600A and without requiring fluid pressure feeding, thus allowing these cables to be installed in HVDC links in very long lengths, up to several hundreds of kilometres. However, due to the remarkable applicability of VSC for HVDC transmissions, which allow the power to be transmitted in both directions without requiring polarity reversal, has allowed re-introducing the use of extruded cables (called XLPE) in DC

power transmission. With the polarity reversal being no longer required, the problem of space charges that can arise with an extruded insulation and create excessive dielectric stress within the cable in the case of sudden polarity reversal is avoided. Extruded insulation offers several remarkable advantages and makes for lighter and easier-to-handle cables, which can operate at high temperatures and at high electrical stresses up to 300kV. The graph in Fig. 1-15 shows the variety of cable systems which could fit best according to the transmission length and voltage.

From the broad range of types described, polymeric cables are usually the preferred choice for HVDC mainly because of their mechanical strength, flexibility and low weight [25].

Based on the electric representation of the cables and depending on the cable model requirements, it is possible to perform more or less simplifications, in order to maintain the accuracy of the model and reduce its complexity. There are two basic transmission line or cable modelling techniques [26]:

- a) Models based on constant parameters: Π models or Bergeron model.

- b) Models based on frequency dependent parameters: modal domain or phase domain.

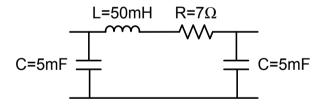

A single  $\pi$  model is used more commonly for normal design and control study in order to model the transients in easy way. If the objective is the analysis of a wide frequency spectrum accurately, a more precise model of a line can be developed considering the distributed parameters and frequency dependent. An example of the simple  $\pi$  model is represented in Fig. 1-16. The parameters for a 100 km line are taken from [26] where the whole analysis regarding the way to obtain them in PSCAD is explained.

Fig. 1-16. Standard  $\Pi$  model using the parameters validated in [26] for a 100km line.

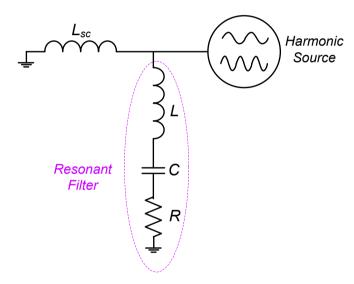

### 1.2.7 Resonant passive filters

An HVDC converter station usually requires ac filters, the purpose of which is to mitigate voltage distortion. On the AC side of a 12-pulse LCC-HVDC converter, current harmonics of the order of 11, 13, 23, 25 and higher are generated. Filters are installed in order to limit the amount of harmonics to the level required by the network apart from compensating to a

certain extent the reactive power. However, with VSC converters there is no need to compensate any reactive power consumed by the converter itself and the current harmonics on the AC side are related directly to the PWM frequency. Therefore the amount of filters in this type of converters is reduced dramatically compared with natural commutated converters.

The passive filters are connected near the transformer to lessen some specific harmonics. The resonant passive filters are constituted by a series connection of a capacitor, an inductor and a resistor, this is, a RLC branch (see Fig. 1-17). The main property of this kind of branch is the delay of 180° between the voltage drop in the inductive impedance and the voltage drop in the capacitive impedance. As a consequence of this characteristic, at the resonance frequency, inductive and capacitive impedances counteract (becoming zero the reactive part of the circuit impedance) and as a result the electric branch only presents the resistive impedance.

Fig. 1-17. RLC resonant filter in parallel with the system.

The RLC branch is tuned to present only the resistive part at the frequency where the harmonic, which is wished to be eliminated, is located. That is achievable by means of infinite combinations of the two independent L and C parameters of the RLC circuit as deduced from (1-1).

$$Z = R + j \cdot \left( 2 \cdot \Pi \cdot f \cdot L - \frac{1}{2 \cdot \Pi \cdot f \cdot C} \right)$$

(1-1)

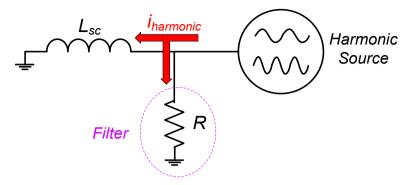

It should be highlighted that to attain a reduction higher than a 50% of any harmonic current with this kind of filters (a RLC branch in parallel with the circuit), the impedance of the filter at the selected frequency has to be less than the impedance presented by the system  $(L_{sc})$  at that frequency. In this way, part of the generated harmonic current is deviated (according to

Kirchoff's law) to the filter instead to flow to the distribution grid or power source as represented in Fig. 1-18.

Fig. 1-18. Simplified RLC filter at the resonance frequency in parallel with the system.

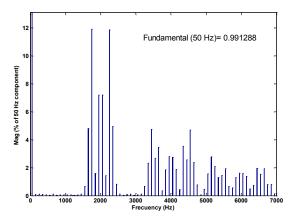

It will be shown later in this report that filters will be dispensable when MMC with high number of submodules is used because the obtained output voltage waveform is of very good quality being its harmonics placed at quite high frequencies.

#### 1.2.8 Electrical grid

It is the main electrical distribution grid to which the energy coming from the wind farm is integrated. It is fundamental to bear in mind that not every world countries have got the same legislation in force what means that the transmission system has to meet the current regulations at the PCC. For that, the onshore substation adapts the voltage, frequency and the reactive power of the transmission system to the voltage level, frequency and reactive power required by the main grid.

#### 1.2.9 Coordinated control system

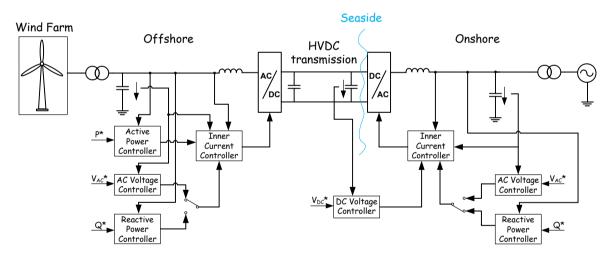

In the case of VSC-based HVDC transmission systems the transfer of power is controlled in the same way as in the case of a classical HVDC transmission [27], the inverter side controls the active power, while the rectifier side controls the DC voltage [28]. One of the advantages of VSC-HVDC is that it makes possible to independently control the active power and the reactive one. Unlike the power transmission between two AC grids in which the power flow can be bidirectional, the VSC-based HVDC system that is used to deliver power from an offshore wind power plant, the active power flow is unidirectional (the offshore side is delivering active power to the onshore side and not vice-versa).

As represented in Fig. 1-9, in a VSC-based HVDC transmission between an offshore WPP and an AC network, two converters are needed: one offshore and another one onshore. Despite not existing direct communication between the two VSC controllers, the objective of

the coordinated system lies in guaranteeing the stability of the whole system. It has to ensure that the energy produced by the wind farm is injected first into the DC link and then transferred into the grid at the onshore side. This entire task has to be accomplished carefully to damp out troublesome oscillations which could disrupt the normal operation of the large interconnected power system.

The offshore HVDC station has the rectifier task which means that all the AC energy delivered by the wind farm is transformed in DC and sent to the land through the DC cables. As shown in Fig. 1-19 the offshore VSC controller maintains the offshore AC inter-turbine grid voltage and frequency. The AC voltage is controlled by the means of the reactive power reference while the frequency is controlled according to the active power which has to be delivered.

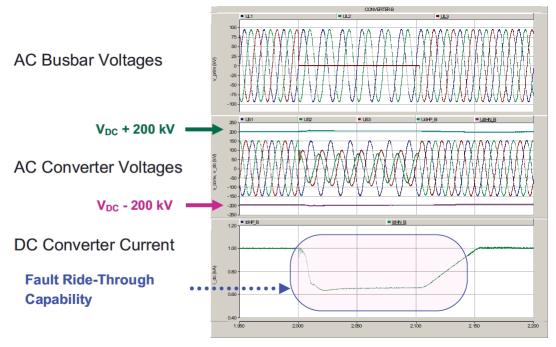

The onshore VSC controller regulates the HVDC bus voltage and the reactive power or AC grid voltage for grid codes compliance [29]. In this case the reference values for the fast inner current controllers are obtained as represented in Fig. 1-19: the DC voltage controller provides the reference value for the active current and the reactive power controller or the AC voltage controller for the reactive current [30].

Fig. 1-19. Overall control structure of the VSC-HVDC transmission system [31].

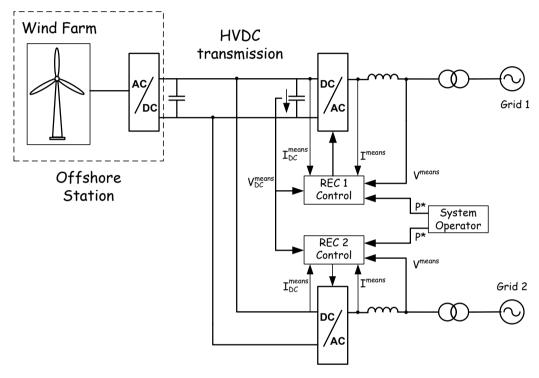

Most of the existing HVDC connection systems in the world are point to point. It means that only one sending-end and one receiving-end stations are available. This kind of connection does not allow the expansion of physical interconnection capacity and improvements of the possibility of power exchange. Nowadays, multiterminal connection (see the diagram represented in Fig. 1-20) is the solution for this lack and it is a suitable solution that can provide the offshore wind farm connection and also that can facilitate the transnational exchange with high cost efficiency [32].

However, when more than one receiving-end station is considered, the control of DC voltages and the power sharing which guarantees the power exchange between the inverter stations can bring some complications. Due to the random behaviour of the wind energy, at any moment is not possible to precisely determine the power which can be delivered. Power converters play an essential role in the safe operation of the system. In order to guarantee the DC voltage balance and power sharing, in [33] three control strategies are compared: scheduled power control, DC voltage droop control and central DC voltage control.

Fig. 1-20. Overall control structure of the MTDC system [34].

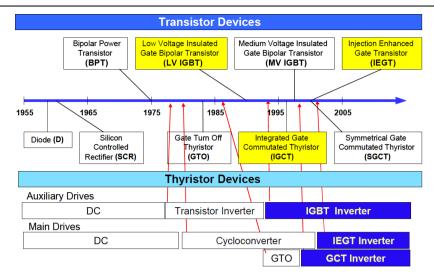

## 1.3 Converter technologies

Along with the development of the power devices, the AC drive system has improved. Fig. 1-21 shows the progress of the power devices and the drive systems development. The diode and thyristor were developed at first. The thyristor was able to turn on the power but the thyristor cannot turn off by itself, so it must be turned off with the help of outside conditions. Then GTO appeared with a function of turn on and turn off capability. Then the GCT/IGCT was developed as fast switching device. Now, the GCT/IGCT is used for large ac drives. And IGBT and IEGT were also developed and now used widely for large ac drives.

Based on the development of the power device and main circuit design, the multilevel inverters are developed and applied in wide range of industries.

Fig. 1-21. Progress of the power devices and the drive systems. Source: [5].

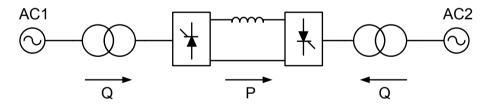

HVDC technologies are often categorised by the power electronic switching device used within the AC to DC converter. **Line commutated current source converters (LCC-CSC)** use thyristor based converters and are capable of achieving high power ratings. Traditionally, it has been the technology for transmitting vast amounts of energy from point to point within an HVDC system (see Fig. 1-22). This tried and tested technology is primarily chosen because of the reliability and robustness inherent within the thyristor valves at the heart of the converter. Over the last decades, progress within the rating and dependability of the thyristor valve has allowed this technique to become more practical and cost effective. It has become the primary technique for medium to long distance electrical transmission with a total of more than 80GW worldwide [35]. However they require a synchronous voltage source to operate due to the limited flexibility inherited within the thyristor valve.

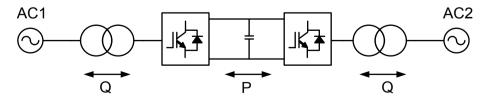

Fig. 1-22. HVDC system based on LCC technology.

Fig. 1-23. HVDC system based on VSC technology.

Recent developments within power electronics have engendered the rise of a contending technology parallel to CSC-LCC. Previously, **self commutated voltage source converters**

(VSC-SCC) had lacked the robustness, plus the high voltage and current rating to be considered for high power transmission. This changed following the development of, amongst others, the Insulated Gate Bipolar Transistor, a device which marries the controllability of the MOSFET with the reliability and power rating of the BJT. The increasing penetration of the power electronics technologies into the power systems is mainly due to the continuous progress of the high voltage high power fully controlled semi conductors. The full controllability and switching symmetry through both turn-on and turn-off operation allows the device to reverse power flow much more quickly than its predecessor. Meanwhile the thyristor can only commute once per cycle, IGBTs can do it several times. This property enables the voltage and current modulation of the converter in order to outage better quality waveforms. Current flowing in the opposite direction is conducted by a reversed diode in parallel to the IGBT. However, this additional component brings a weakness to the system when a fault occurs on the DC side by creating a path for the resulting fault current.

Fig. 1-24. a) First HVDC thyristor valve (1967). b) The world's first 12-pulse converter (1976). Source: ABB [23].

It is useful to consider some of the advantages the VSC transmission system offers [36]:

- The ability to control reactive and active power independently.

- The link is operational with weak AC systems.

- No commutation failures within the converter.

- Black-start capability.

- No polarity reversal required to reverse the power flow direction which has a positive effect on the isolation of the conductors.

- The modularity of the converter reduces manufacturing costs, facilitates maintenance and permits provisions for spare parts.

- With the use of intercycle PWM switching, or multi-level configurations in the VSC schemes, the filter requirements are drastically reduced or even eliminated altogether.

| Project<br>Name                  | Commissioning year | Power rating                        | No. of circuits | AC voltage                                       | DC<br>voltage | Length of DC cable                        | Reasons for choosing<br>HVDC                                                                                     | topology |

|----------------------------------|--------------------|-------------------------------------|-----------------|--------------------------------------------------|---------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------|

| Hällsjön,<br>Sweden              | 1997               | 3 MW<br>±3MVAR                      | 1               | 10 kV<br>(both ends)                             | ± 10 kV       | 10 km<br>Overhead lines                   | Test transmission.<br>Synchronous AC grid                                                                        | 2L       |

| Gotland<br>HVDC light,<br>Sweden | 1999               | 50 MW<br>-50 to<br>+55MVAR          | 1               | 80 kV (both ends)                                | $\pm~80~kV$   | 2×70 km<br>Submarine cables               | Wind power (voltage<br>support). Easy to get<br>permission for<br>underground cables.                            | 2L       |

| Eagle Pass,<br>USA               | 2000               | 36 MW<br>±36MVAR                    | 1               | 138 kV<br>(both sides)                           | ± 15.9 kV     | Back to back HVDC light station           | Controlled<br>asynchronous<br>connection for trading.<br>Voltage control. Power<br>exchange                      | 3L-NPC   |

| Tjaereborg,<br>Denmark           | 2000               | 8 MVA<br>7.2 MW<br>-3 to +4<br>MVAR | 1               | 10.5 kV (both sides)                             | ± 9 kV        | 4×4.3 km<br>Submarine cables              | Wind power. Demonstration project.                                                                               | 2L       |

| DirectLink,<br>Australia         | 2000               | 180 MW<br>-165 to +90<br>MVAR       | 3               | 110 kV<br>(Bungalora)<br>132 kV<br>(Mullumbimby) | ± 80 kV       | 6×59 km<br>Underground cable              | Controlled<br>asynchronous<br>connection for trading.<br>Easy to get permission<br>for underground<br>cables.    | 2L       |

| MurrayLink,<br>Australia         | 2002               | 220 MW<br>-150 to 140<br>MVAR       | 1               | 132 kV (Berri)<br>220 kV<br>(Red Cliffs)         | ± 150 kV      | 2×180 km<br>Underground cable             | Controlled<br>asynchronous<br>connection for trading.<br>Easy to get permission<br>for underground<br>cables.    | 3L-ANPC  |

| CrossSound,<br>USA               | 2002               | 330 MW<br>±150MVA<br>R              | 1               | 345 kV<br>(New Heaven)<br>138 kV<br>(Shoreham)   | ± 150 kV      | 2×40 km<br>Submarine cables               | Controlled connections for power enhance. Submarine cables.                                                      | 3L-ANPC  |

| Troll<br>offshore,<br>Norway     | 2005               | 84 MW<br>-20 to +24<br>MVAR         | 2               | 132 kV<br>(Kollsnes)<br>56kV (Troll)             | ± 60 kV       | 4×70 km<br>Submarine cables               | Environment, long<br>submarine cable<br>distance, compactness<br>of converter on<br>platform<br>electrification. | 2L       |

| Estlink,<br>Estonia-<br>Finland  | 2006               | 350 MW<br>±125MVA<br>R              | 1               | 330kV (Estonia)<br>400kV (Finland)               | ± 150 kV      | 2×31 km Underground<br>2×74 km Submarine  | Length of land cable,<br>sea crossing and non-<br>synchronous AC<br>systems.                                     | 2L       |

| Caprivi<br>Link,<br>Namibia      | 2009               | 300 MW                              | 1               | 330kV Zambezi<br>400kV Gerus                     | 350 kV        | 970 Overhead lines                        | Synchronous AC grid,<br>long distance, weak<br>networks                                                          | -        |

| Valhall<br>offshore,<br>Norway   | 2009               | 78 MW                               | ſ               | 300 kV (Lista)<br>11kV (Valhall)                 | 150 kV        | 292 km<br>Submarine cables                | Reduce cost and<br>improve operation<br>efficiency of the field.<br>Minimize emission of<br>green house gases.   | 2L       |

| BorWin1,<br>Germany              | 2012               | 400 MW                              | 1               | 380 kV Diele<br>170kV Borkum<br>2                | ± 150 kV      | 2×75 km Underground<br>2×128 km Submarine | Offshore wind farm,<br>length of land and sea<br>cables, asynchronous<br>system                                  | -        |

Table 1-3. Summary of worldwide VSC-HVDC projects and their basic parameters.

The recommended converter technology varies depending on the application. Although there is not a well-defined range, the previous Fig. 1-7 represents an approach of the optimum technology according to the application power and transmission distance. So, as indicated in the figure, from 500 MW on conventional HVDC is more favourable than VSC based HVDC. In Table 1-3 some of the worldwide HVDC-VSC projects are collected.

## 1.4 HVDC-VSC topologies

The VSC HVDC technology using IGBTs recently has gained growing interest due to its simplified modularity and flexibility due to the four-quadrant operation of the converter. One of the main advantages of VSC-based transmission is its ability to control reactive power in both directions, independently of the real power flow. Except for the maximal rating power (which is limited in VSC HVDC to around 500 MW while single LCC HVDC link can possibly transmit more than one GW power [37]), this second topology has superior advantages. That is why from the two converter technologies explained before, this study will be focused on the second one, VSC.

This section deals with a number of VSC topologies suitable for HVDC transmissions. In addition to those topologies and control philosophies already developed by major manufacturers, along this document some variations will be introduced.

#### 1.4.1 Two level converter

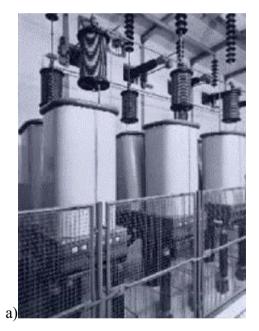

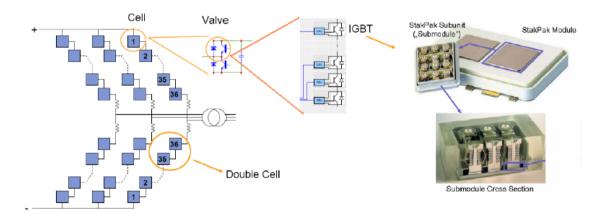

HVDC Light conversion system [38] was first introduced by ABB in 1997. It is based on a two level topology meaning that the output voltage is switched between two voltage levels. As can be seen in Fig. 1-25, each phase has two valves, one between the positive potential and the phase terminal and the other between the phase terminal and negative potential. Thus, a three phase converter has got six valves, three phase reactors and a set of DC capacitors. To be able to switch voltages higher than the rated voltage of one IGBT, several positions are connected in series in each valve. A complete IGBT position consists of a StakPak IGBT, a reversing diode, a gate unit, a voltage divider and a water-cooled heat sink [39].

HVDC Light uses a sinusoidal based PWM control philosophy to control the IGBT's gate switching frequency producing a two level AC waveform. This is then improved to a sinusoidal form by the phase reactors. To eliminate harmonics, they are concentrated into a narrow band where small filters can be used. The series connected IGBT's need to switch at exactly the same moment, to do this the voltage over each individual IGBT is measured and a

boost signal is provided to the gate of the transistor depending on the measured voltage. The monitoring system for the IGBT states is managed by a patented ABB control technology.

Fig. 1-25. Schematic of a three phase 2 level HVDC-Light converter with series connected positions in each valve.

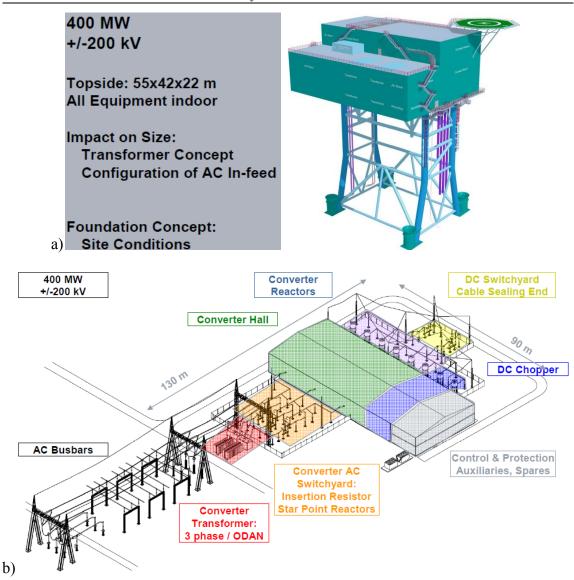

The latest example of a HVDC Light application is the Borkum 2 (Germany) offshore wind farm transmission which is in operation since 2009. The transmission capacity is 400 MW at ± 150kV DC voltage by 128 km of extruded polymer insulated submarine cables. The receiving station on land is located at Diele, 75 km from the coast, where the power will be injected into the German 380kV grid [38].

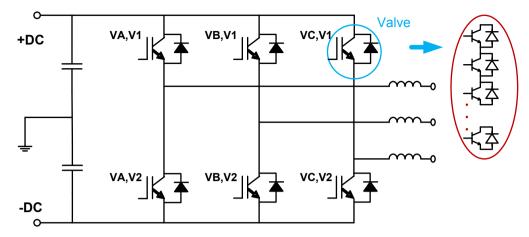

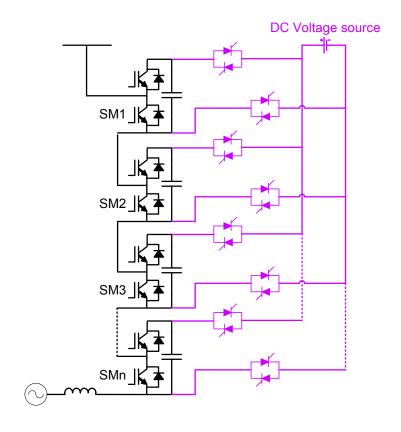

#### 1.4.2 Modular Multilevel Converter (MMC)

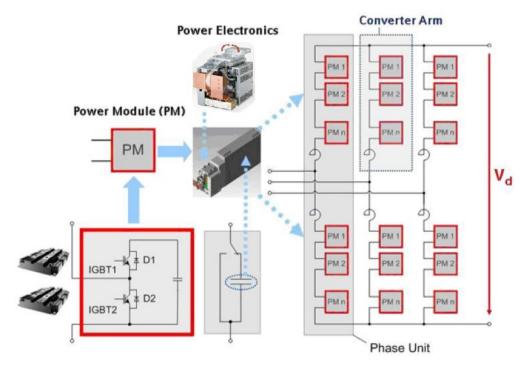

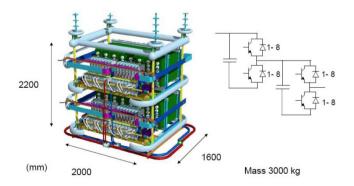

Fig. 1-26. SIEMENS' Modular Multilevel Converter main circuit. Source: [40].

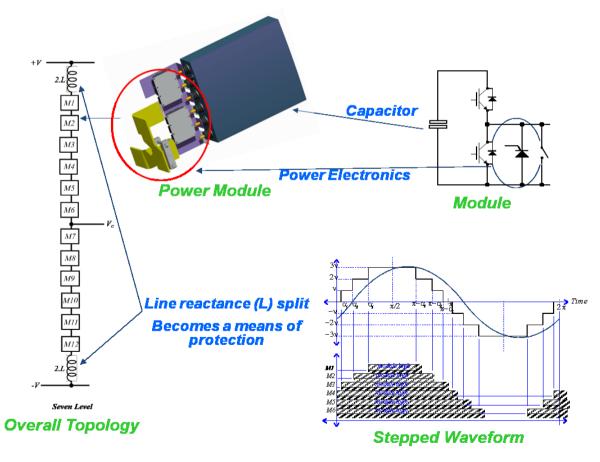

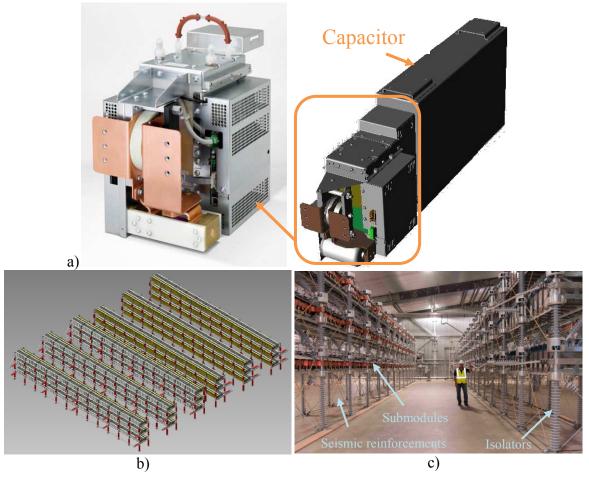

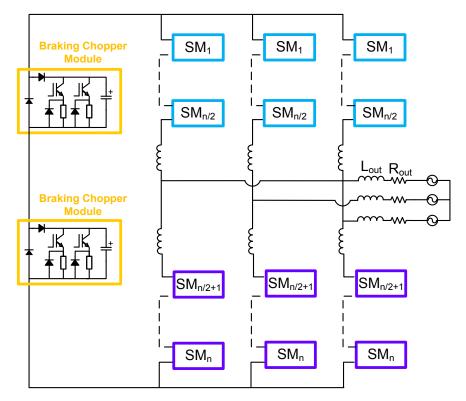

An alternative approach is Siemens' last technology and control system referred to as HVDC Plus [41] which uses multilevel converters (see the three phase schematic in Fig. 1-26). It consists of six converter legs, whereas the individual converter leg consists of a series connection of power modules (PM) connected in series with one converter reactor. Each of the submodules contains an IGBT half bridge as switching element and a DC storage capacitor. The two converter legs of each phase module represent a controllable voltage source because it is possible to separately and selectively control each of the individual submodules. The total voltage of the two converter legs in one phase unit equals the DC voltage, and by adjusting the ratio of the converter leg voltages in one phase module, the desired sinusoidal voltage at the AC terminal can easily be achieved. The AC waveform is built using small voltage steps formed by controlling the modules which are turned off or turned on at any given instant. Therefore there is very small need for AC voltage filtering to achieve a sinusoidal waveform in comparison to a two level circuit. This approach of using modules maximises the output voltage of the converter as many modules can be used in series [42]. The first project to use HVDC Plus came online in November of 2010 and is called the Trans Bay Cable in California.

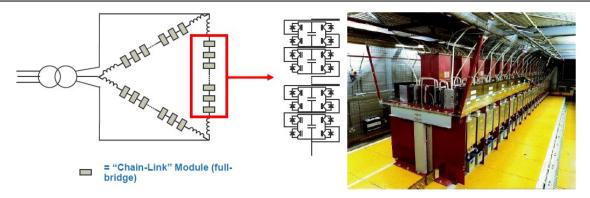

Fig. 1-27. Alstom Grid's Chain-link converter based VSC-HVDC main equipment. Source: [40].

Fig. 1-28. Alstom Grid's STATCOM based on the MMC or "chain circuit": circuit arrangement (left) and one phase of a ±75MVAr STATCOM supplied for National Grid's East Claydon substation. Source: [43].

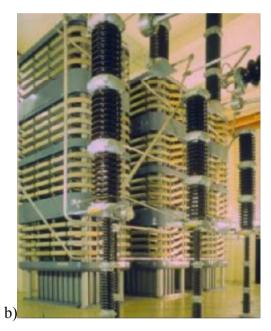

Two other prominent manufacturers, Alstom Grid and ABB, have developed very similar Modular Multilevel Converters (MMC) known by the commercial trade names Chain-Link and Cascaded Two Level converter (CTL) [44] respectively. This fact is evidenced by Fig. 1-27 and Fig. 1-29 where little differences in the arrangement can be found. However, it has to be highlighted the fact that in CTL series-connected press-pack IGBTs are used in the valves, thus extending a technology which successfully has been used for high voltage two-level VSCs to multilevel VSCs through cascade connection.

Fig. 1-29. Outline of ABB's Cascaded Two-Level (CTL) converter. Source: [45].

Fig. 1-30. Cell module with two valves, each comprising eight series-connected press-pack. Source: [45].

Fig. 1-31. Mechanical outline of ABB's CTL double submodule. Source: [45].

Apart from these two converter topologies, another possible option is the series-parallel connection of converters using transformers. This topology lies in assembling conventional VSC in series or parallel connection using transformers with the aim of reaching the required voltage and current values avoiding the necessity of designing an exclusive converter to fulfill the application requirements. Some configurations appear in patents such as [46] or [47]. However, there is not any known HVDC application in which it has been applied despite being an alternative for the two previous explained topologies.

### 1.5 Purpose of the thesis

As has been introduced, this thesis was within the framework of the study of electronic power converter topologies oriented to the HVDC transmission of the power generated in offshore wind farms, focusing the research on the Modular Multilevel Converter (MMC) topology. There have been two general objectives pursued in this thesis:

- To study, analyse, compare and evaluate the MMC comprised of different submodule topologies.

- To propose a capacitors voltage balancing algorithm, which can be applied to the MMC with different submodule topologies.

To accomplish these objectives it is necessary to model the converter, to simulate it in Matlab software and then to built a downscaled real test bench in the laboratory to contrast the simulation results with the experimental ones.

## 1.6 Description of the chapters

This thesis is divided into seven chapters, appendixes and bibliography. The content of these chapters is summarized below:

<u>Chapter 1</u>: the opening chapter reviews the current situation and trends of the wind energy as well as wind farms. Then a HVDC transmission from an offshore wind farm to the onshore substation is thoroughly described. From all the elements which make that energy transmission possible, this thesis is focused on the converter, that is why a brief state of the art of power converter technologies and topologies is exposed. Finally the objectives pursued by this thesis are presented.

<u>Chapter 2</u>: this chapter studies deeply the Modular Multilevel Converter with three different submodule concepts: 2L half bridge, 3L-FC and 3L-NPC. The converter is modelled by means of differential equations, the way of implementing the modulation technique is explained and some simulation results are shown. In addition, a methodology to size the converter capacitors and inductances is presented. Although the total voltage of the submodules is controlled, at the end of the chapter the individual capacitors unbalancing problem is raised.

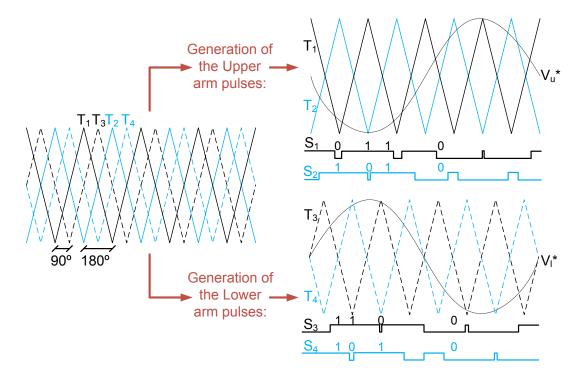

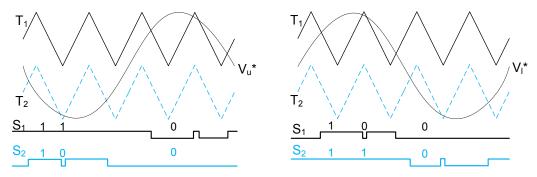

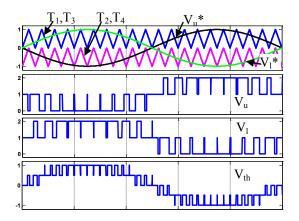

Chapter 3: Despite the fact that any modulation technique applicable to multilevel converters is also valid for MMC, along this chapter a modulation algorithm based on phase shifted PWM which copes with the capacitors unbalances is introduced. Firstly the general modulation philosophy is explained applied to the 2L submodule concept and then it is extended to 3L-FC, and 3L-NPC submodule topologies. Its effectiveness is confirmed by simulation results at different modulation indexes,  $cos(\varphi)$ , number of submodules per phase and switching frequency.

<u>Chapter 4</u>: in the fourth part of the report, the validation of the previously developed modulation strategy is carried out by means of successful experimental results obtained in a downscaled laboratory setup. The capacitors balancing at any operation condition are corroborated with submodules 2L and 3L-FC topologies.

<u>Chapter 5</u>: A comparative assessment based on thermal analysis and sizing of the converter elements is made, revealing the benefits and drawbacks of using the studied different submodule concepts (including the 2L half bridge submodules with series connection of several controlled switches) and the conclusions drawn therefrom.

<u>Chapter 6</u>: On the one hand, this chapter deals with technical difficulties associated to the implementation and the structure of the converter. On the other hand, breakdown and failure protections for the system are proposed. Especially an analysis concerning the consequences of malfunctions in submodules is carried out.

<u>Chapter 7</u>: General conclusions and main contributions of the thesis as well as future work are summarized.

# Chapter 2

## **Modular Multilevel Converter (MMC)**

From the three converter topologies explained before, the decision as to continue studying in depth the MMC topology has been made. This converter topology has arisen as the leader and most competitive solution for VSC applications operating in the range of high power and high voltage levels [48]-[52]. Transmission of energy by means of HVDC seems to be an application area with an attractive future for this kind of converter topology [44], [53]-[54]. The main characteristics and most important features of this converter are summarized and discussed in publications such as [56]-[61], being its scalability or modular structure and its transformerless nature, probably its major advantages [61]-[62]. Due to these reasons, the MMC provides a suitable and flexible converter design that can be adapted to different ranges of voltages and powers.

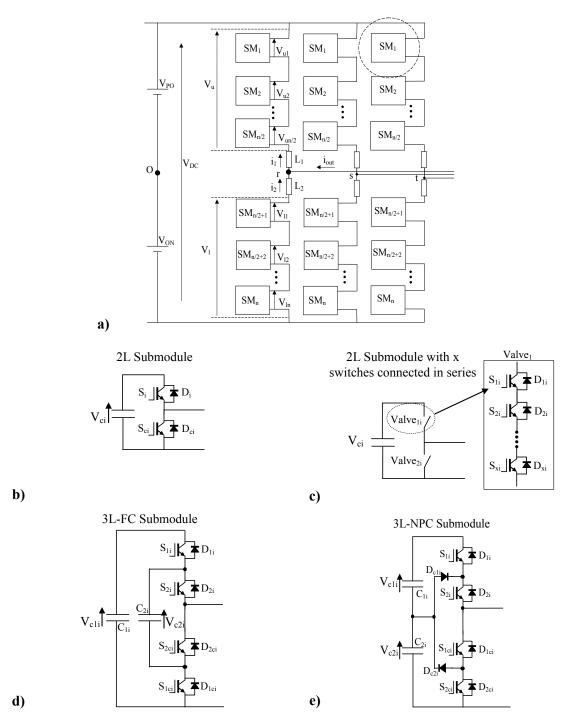

Although the majority of the published papers have been focused on MMC designs with two level half bridge submodules [48]-[64], it is also possible to arrange MMC topologies using multilevel submodule concepts, as reported for instance in [65]. Note that under this situation, we can find many possible submodule concepts, just combining the multilevel topology chosen, for example Flying Capacitor (FC), Neutral Point Clamped (NPC), Multi Point Clamped (MPC), Neutral Point Piloted (NPP), etc... and the number of levels used: 3, 4, 5, etc...[59]. This innovative solution, can be interesting for example from a manufacturer perspective, in order to bring already existing and well proven multilevel submodule designs to novel MMC arrangements, or simply to achieve a better usage of the trade components such as the semiconductors. In addition, it can help solving protecting actions taken by different manufacturers related to patents. On the other hand, from a construction point of view, using multilevel

modules is advantageous in reducing the dimensions of the whole converter at expenses of complicating the technology of the submodule.

Therefore, in this thesis besides studying the MMC with 2L submodules, the same converter with unconventional submodules will be researched. Obviously not all the topologies will be considered, only two of the multilevel: the well known 3 Level NPC and the 3 Level FC based submodule concepts.

Along this chapter, first the basic operation of the converter as well as the mathematical behavioural modelling of the MMC with 2L submodules is described. The modelling of the MMC has been carried out through differential equations because it is essential to learn in depth the behaviour of the converter but it is also useful for developing the control of the system and choosing the most suitable modulation technique. Secondly how the modulator generates the switching pulses for the semiconductors using PWM is explained. Then some simulation results are exposed to clarify the previous concepts. The same steps have been followed for the MMC with 3L-FC and 3L-NPC submodules.

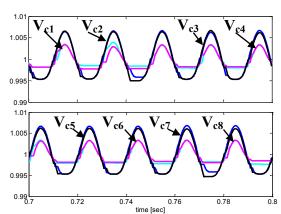

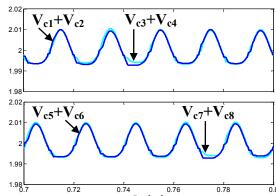

A sizing methodology for the passive components of the converter (the inductances and capacitors) is also included. After that, the way of controlling the voltage of all the submodules of the converter is presented. Despite employing this control method, the balancing problems which appear in the submodules capacitors will be discussed. To end up, the obtained conclusions of the chapter are provided.

#### 2.1 MMC with 2L submodules

#### 2.1.1 Modelling

The aim of modelling the converter by means of differential equations is first to describe its behaviour taking into consideration that all the switches are ideal. This helps develop a deeper understanding of the performance of the system. Moreover, thanks to the mathematical model the converter can be simulated, the different control loops designed and the suitable modulation technique chosen.

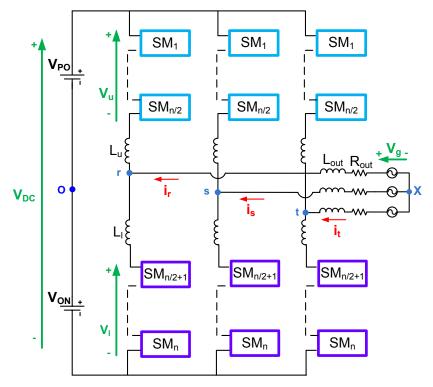

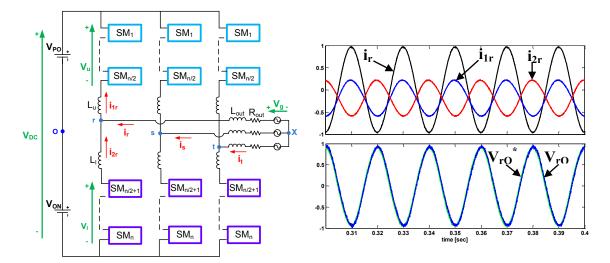

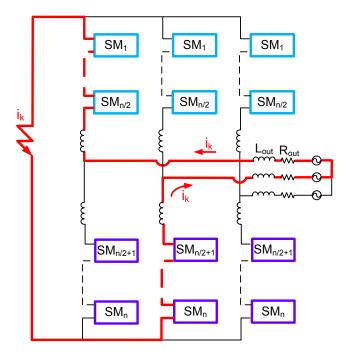

Fig. 2-1. Layout of the three phase MMC.

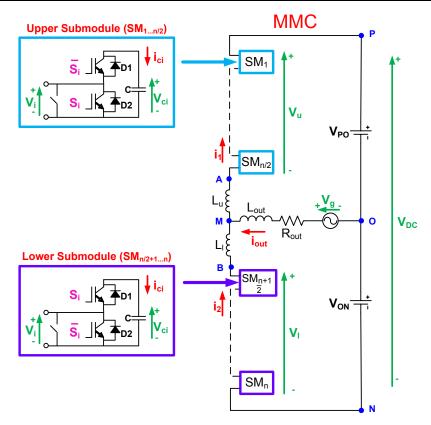

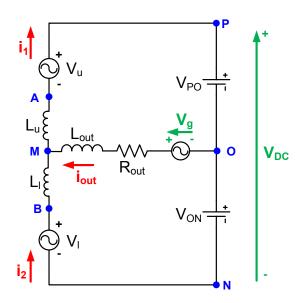

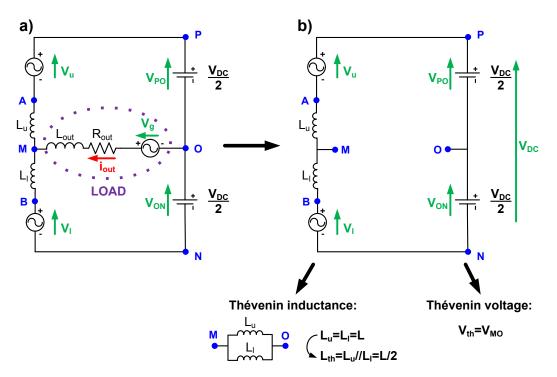

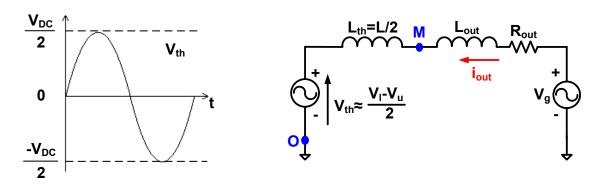

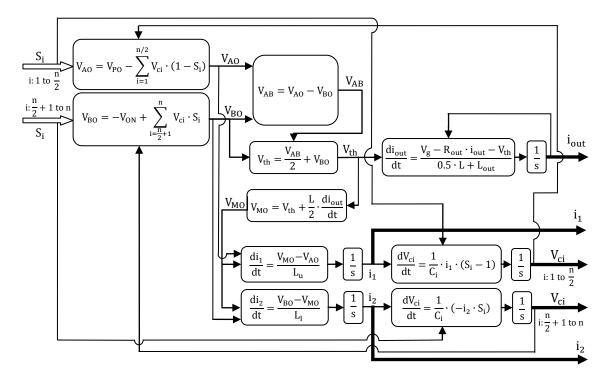

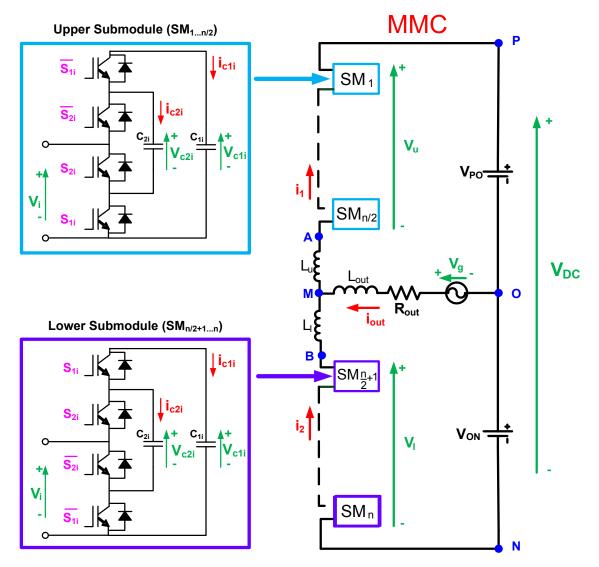

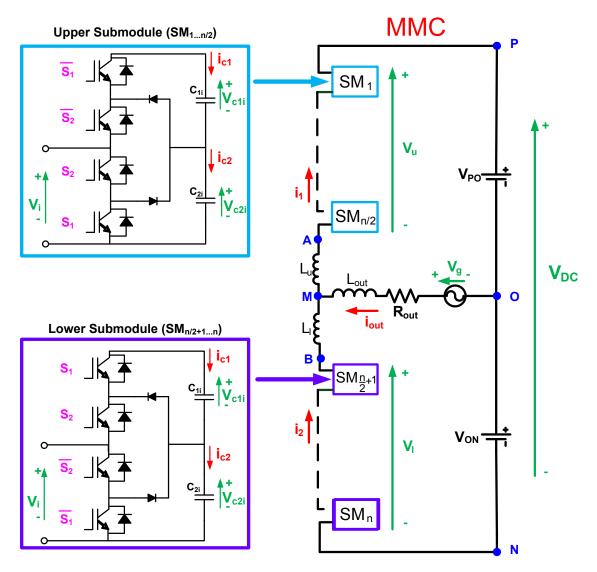

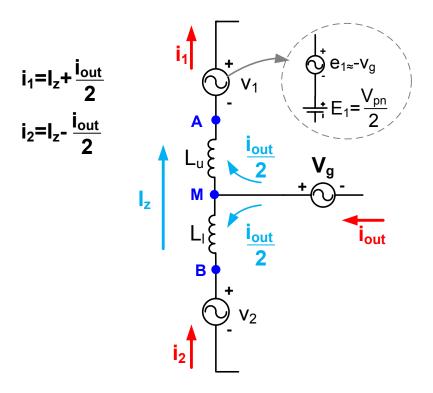

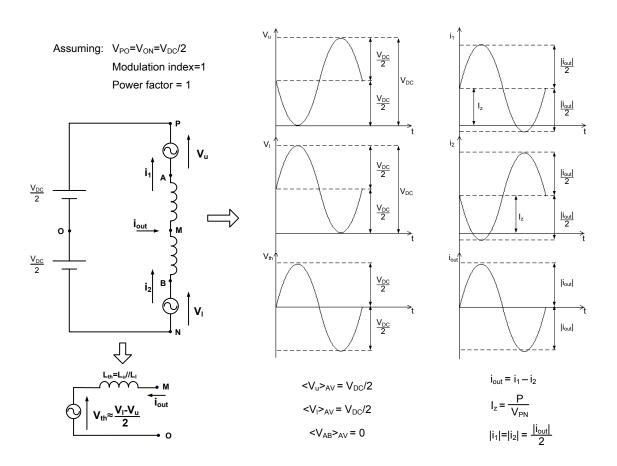

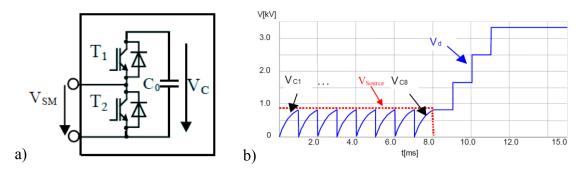

The layout of the three phase Modular Multilevel Converter is shown in Fig. 2-1. The converter consists of three identical phase units, each with upper and lower multivalves. However, for the following developments, the simplest structure will be considered, this is, the single phase converter with n submodules shown in Fig. 2-2. It consists of two arms of converter, each one formed by a n/2 series connected power submodules plus an inductor or filter that can adopt several configurations [53]. Each submodule contains two insulated-gate bipolar transistors (IGBT), two reversing diodes and a DC energy storage capacitor. The DC side is modelled by two DC voltage sources (considered as constants in this study  $V_{PO} = V_{ON} = V_{DC}/2$ ), while the AC side between terminals M and O is modelled by an AC voltage source ( $V_g$ ), a resistor ( $R_{out}$ ) and an inductor ( $L_{out}$ ). Both arm inductors and the output one are taken to be linear and without internal resistance.

Fig. 2-2. Layout of the single phase MMC.

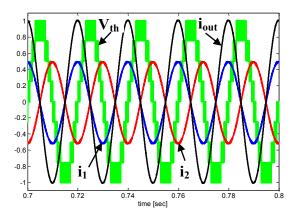

Once the layout of the converter is shown, the purpose of the following analysis is to work out the differential equations which describe the dynamic of the different variables of the converter: the voltage of every capacitor  $(V_{ci})$ , the two arms currents  $(i_1 \text{ and } i_2)$  and the output current  $(i_{out})$ . These four variables will be a function of the steady ones or the conduction state of all the switches. Being the configuration of the upper and lower arm submodules identical, note that along the next discussion, their firing commands are considered opposite between them (see Fig. 2-2). The reason of this choice will be later explained but it should be taken into account on the whole system.

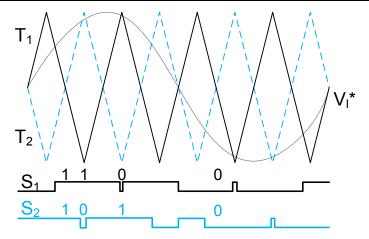

In normal operation, only one of the two semiconductors is on at a given time instant, that is why each submodule toggles between two states. In the upper arm submodules, on state  $(S_i=1)$  represents that the lower semiconductor is conducting but not the upper one, whereas off state  $(S_i=0)$  means that the upper semiconductor is conducting but not the lower one. Assuming that the capacitor voltage is  $V_{ci}$ , the output voltage  $V_i$  of each power submodule can take one of the two different voltage levels. When the submodule state is on, the voltage within submodule terminals is zero but when it is off the submodule is outputting  $V_{ci}$ . In order to make everything clear, in Table 2-1 the voltage at submodules terminals is exposed, as well as the current that circulates along the capacitor for both upper and lower arms and switching states.

| Upper arm |          |                 |                    |                   |  |

|-----------|----------|-----------------|--------------------|-------------------|--|

| $S_i$     | $V_{i}$  | i <sub>ci</sub> | i <sub>1</sub> >0  | i <sub>1</sub> <0 |  |

| 0         | $V_{ci}$ | -i <sub>1</sub> | $V_{ci}\downarrow$ | $V_{ci} \uparrow$ |  |

| 1         | 0        | 0               | $V_{ci} \approx$   | $V_{ci} \approx$  |  |

| Lower arm |          |                 |                     |                   |  |

|-----------|----------|-----------------|---------------------|-------------------|--|

| $S_i$     | $V_{i}$  | i <sub>ci</sub> | i <sub>2</sub> >0   | i <sub>2</sub> <0 |  |

| 0         | 0        | 0               | $V_{ci}\approx$     | $V_{ci} \approx $ |  |

| 1         | $V_{ci}$ | -i <sub>2</sub> | $V_{ci} \downarrow$ | V <sub>ci</sub> ↑ |  |

Table 2-1. Switching states, voltage and currents of 2L submodules.

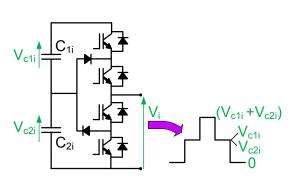

Therefore, it is possible to selectively and separately control each of the individual submodules in the converter to provide a voltage which is either  $V_{ci}$  or zero. Remembering that each converter arm is formed by a series connection of several submodules, the voltage obtained in the n/2 upper submodules of the phase is the result of adding up the individual voltages and is called  $V_u$  (2-1). Likewise the voltage obtained in the n/2 lower submodules of the phase is  $V_l$  (2-2). Notice that these two equations depend on the switching state of every submodule and thus their value will be varying continuously according to those switching states. This is the reason why in the simplified diagram of Fig. 2-3 upper and lower submodules have been replaced by some alternative voltage sources.

$$V_{u} = \sum_{i=1}^{n/2} V_{ci} \cdot (1 - S_{i})$$

(2-1)

$$\mathbf{V}_{l} = \sum_{i=n/2,l}^{n} \mathbf{V}_{ci} \cdot \mathbf{S}_{i} \tag{2-2}$$

Fig. 2-3. Simplified diagram of the single phase MMC.

Looking at Fig. 2-3, the voltage between different points of the circuit which depends on the state of all submodules is calculated, where n refers to the total number of submodules per phase:

$$V_{AO} = V_{PO} - V_{u} = V_{PO} - \sum_{i=1}^{n/2} V_{ci} \cdot (1 - S_{i})$$

(2-3)

$$V_{BO} = -V_{ON} + V_{I} = -V_{ON} + \sum_{i=n/2}^{n} V_{ci} \cdot S_{i}$$

(2-4)

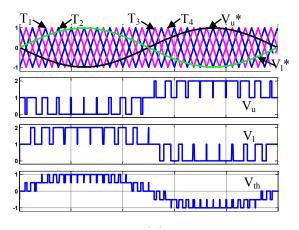

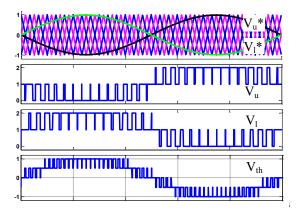

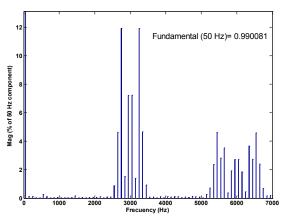

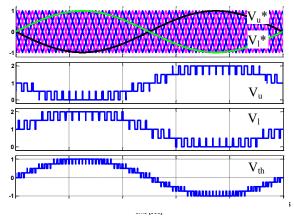

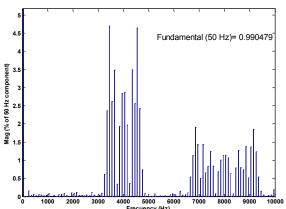

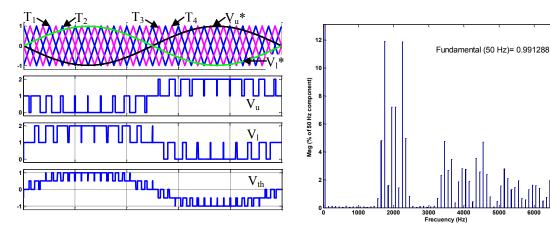

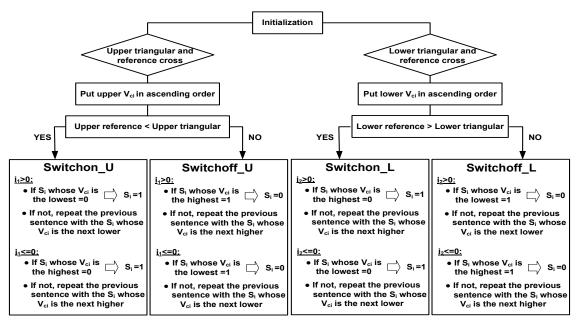

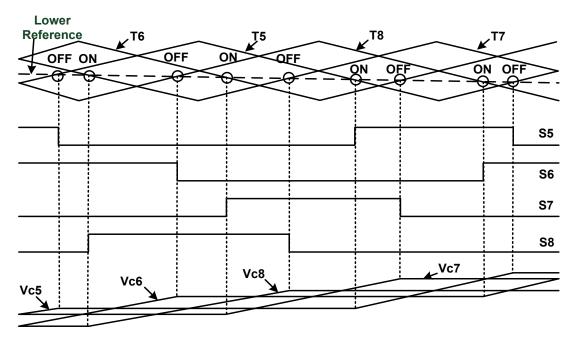

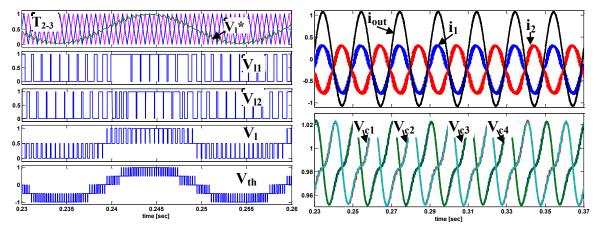

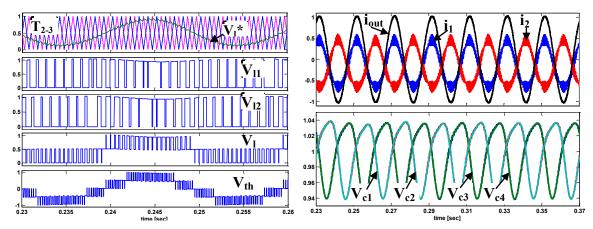

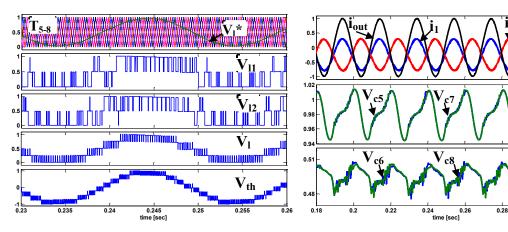

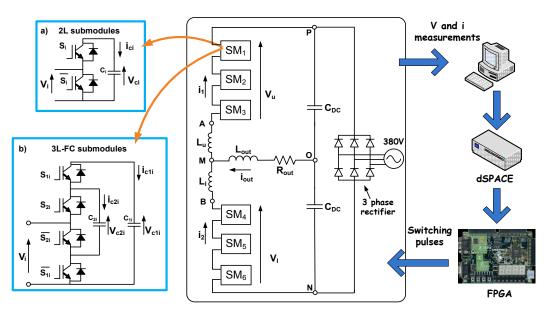

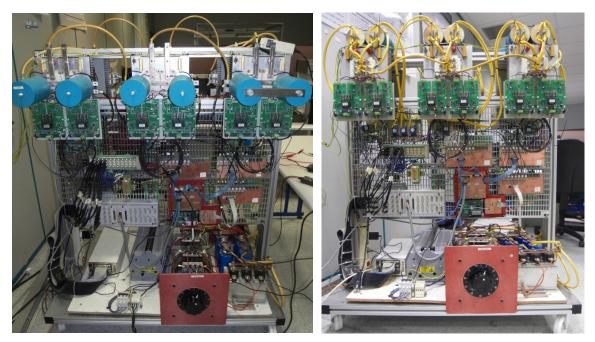

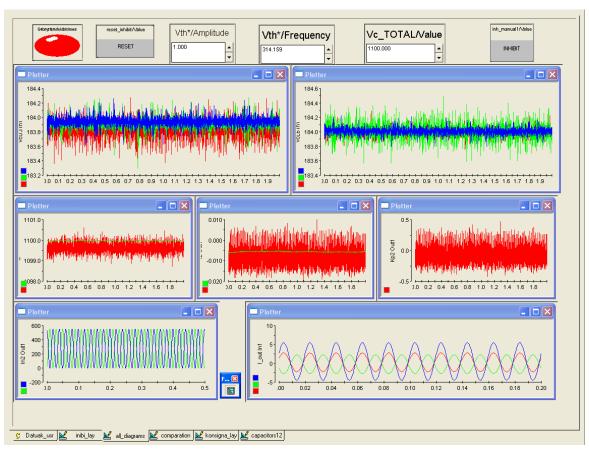

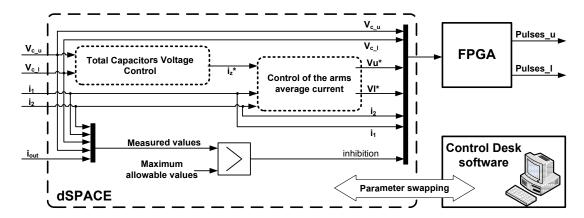

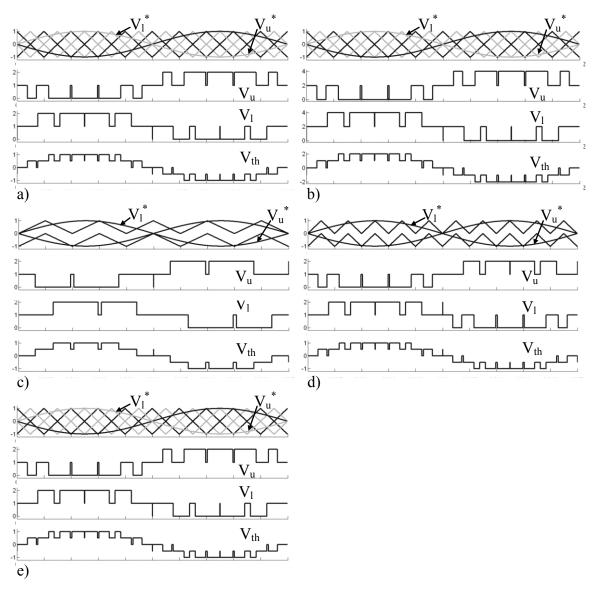

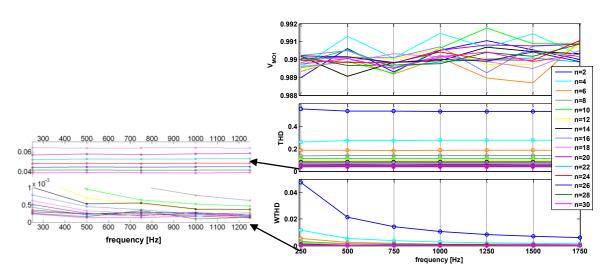

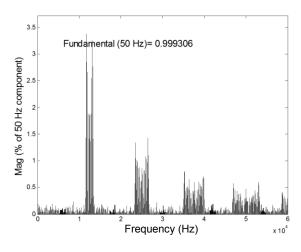

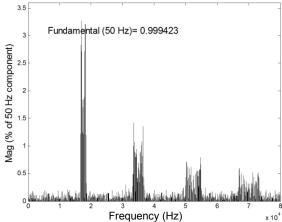

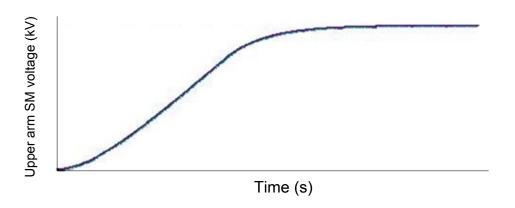

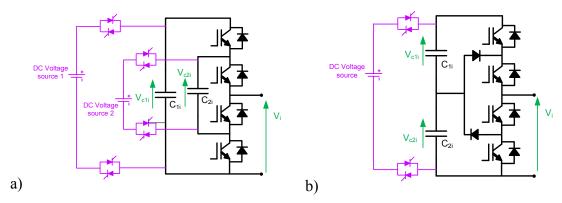

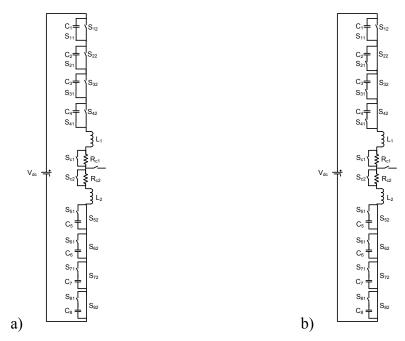

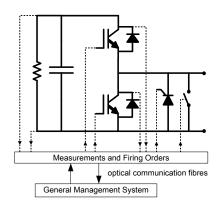

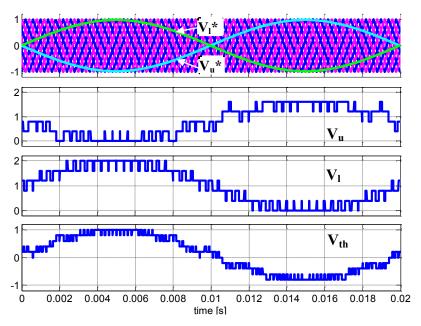

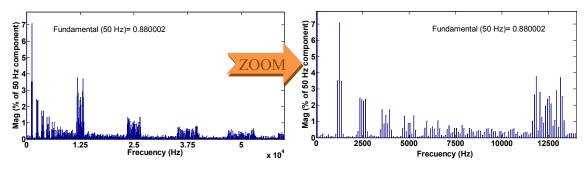

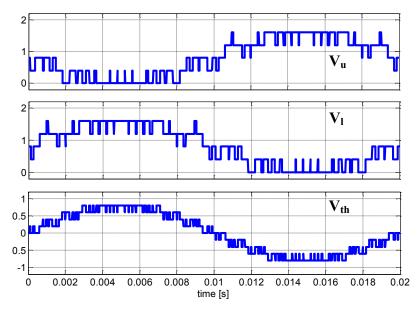

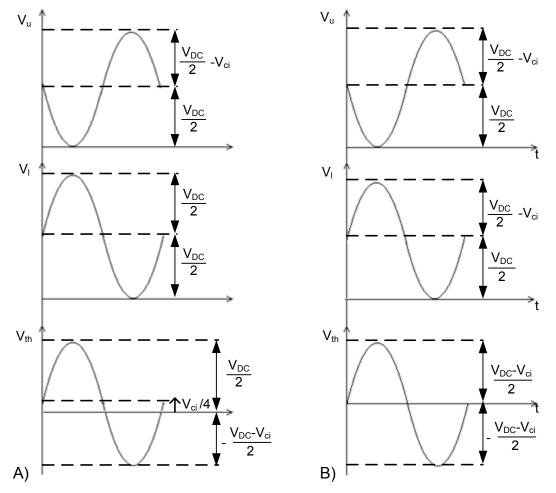

Subtracting the previous equations the voltage  $V_{AB}$  is achieved: