### **DOCTORAL THESIS**

PARTIAL POWER CONVERTERS FOR DC-DC APPLICATIONS

# Partial Power Converters for DC-DC Applications

PhD Student: JON ANZOLA GARCÍA

Supervisor: IOSU AIZPURU LARRAÑAGA

Mondragon Goi Eskola Politeknikoa

Mondragon Unibertsitatea

Hernani (Gipuzkoa), December 2022

### ACKNOWLEDGEMENTS

I would like to first and foremost thank my director Dr. Iosu Aizpuru Larrañaga who trusted me and gave me the opportunity to carry out this thesis. Because of his catching and inspiring attitude, his endless passion and excitement for power electronics, and his countless creative and excellent ideas, Dr. Iosu was essential to achieve the results of this work. Iosu, I feel very grateful for being under your guidance through the last 4 years.

I would also like to thank to Asier Arruti, who selflessly dedicated plenty of his time to help me on the design and testing of every single prototype presented in this work. All his technical advices were of vital importance when there were problems to go ahead. Asier, I have enjoyed all the interesting on- and off-topic discussions we had every day at the lab.

I would also like to thank to my colleagues Santi, Miguel and Anartz, who offered me their help in the assembly and testing of the prototypes and devices presented in this work. I cannot thank you enough your support and kindness.

My gratitude is also extended to North Carolina State University and especially to the people working in the department conducted by Professor Subhashish Bhattacharya at FREEDM Systems Center. Thank you very much for giving me the opportunity to make a stay of 5 months with such a talented team. Also, I would also like to make a special mention to Shrivatsal Sharma, who patiently guided and advised me during my stay at their lab.

I would also like to acknowledge colleagues from Universidad de Zaragoza, Sergio, Carlos, Fran, Estanis, Ivan, and Miguel for the opportunity to collaborate with them. It is always a pleasure to work with you.

Also, I want to thank each member of the jury for taking their time to review the document, come to the thesis defense event, and for giving me their point of view about the developed work. I feel very proud and grateful for receiving the comments and the point of view of such an exceptional jury.

Good office mates are a key factor for a successful PhD and I must admit that I could not be more fortunate. Colleagues like Oier, David, Antxon, Iñaki and Javi accompanied me since the very first day and after all the time shared together, I like to think we built a good friendship. Later, Iker, Xabi, Yerai, Borja, Miriam, Itxaro, Manu, Josu, Manex, Maite... joined the team and the PhD room got completely filled. It is always nice to see young, motivated and talented researches like you every day at the office. I would also like to extend my gratitude to Claudio, Stefano and Andrew, who made me feel closer to home during my stay at the United States. Thank you very much to all of you for the working atmosphere and for not taking everything too serious. I

appreciated a lot the interesting and helpful discussions (also non-work related) and social happenings with you.

Of course, I cannot forget many other people from Galarreta, Unai, Canales, Erik, Asier, Argiñe, Mazu, Ander, June, Eneko, Ane, Jaione, Isak... other workmates from Arrasate, Manex, Igor, Ramon, Eneko, Julen... It is great to see such a healthy working atmosphere between our groups.

Eskerrik asko bihotzez Mondragon Unibertsitatetik kanpoko lagunei: PCT-ko lagun guztiei, Ñoñostiko kuadrillari eta Batalloneko kamaradei. Benetan lagundu nauzuela Tesisetik deskonektatzera eta aurrean nituen erronkei energia berriekin aurre egitera.

Por último, me gustaría agradecer a mis padres Rafael y Regina por todo el apoyo y los ánimos que me han dado siempre. Gracias ellos he tenido la oportunidad de estudiar lo que he querido y donde he querido, sin preocuparme de nada más. También quiero darle mi agradecimiento a mi hermana Arrate, que siempre me ha ofrecido su apoyo moral cuando lo he necesitado.

Hernani, December 2022

Jon Anzola García

## CREATIVE COMMONS LICENSE

**Recognition – No-Comercial – Share-alike (BY–NC–SA):** The license does not allow commercial use of the original work or any derivative works. The distribution of the derivative work must be made under a license equal to that governing the original work.

## ABSTRACT

This thesis studies partial power processing (PPP) based architectures for DC-DC applications. This type of solutions aim to reduce the power processed by the power converter. This way, the power losses and the volume of the power converter is reduced.

The work starts with an overview on the PPP strategies. In this sense, the different solutions found in the literature are classified into three main strategies: differential power converters, partial power converters (PPC) and mixed strategies. Due to their numerous applications and high efficiency results, the thesis focuses on the PPC architectures.

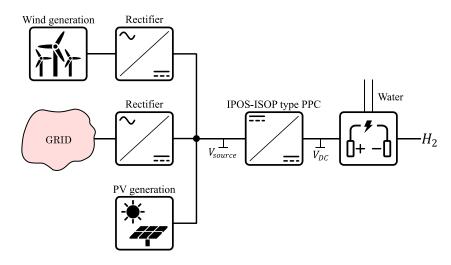

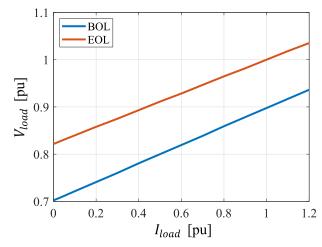

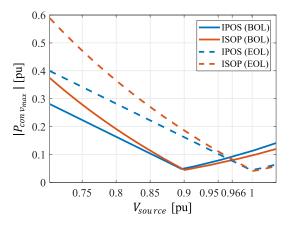

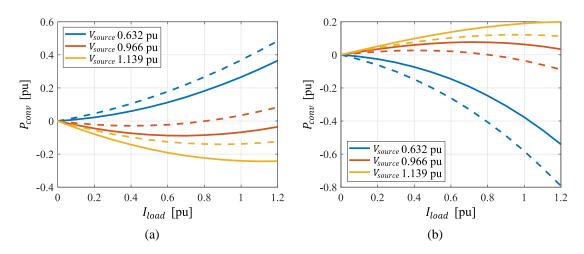

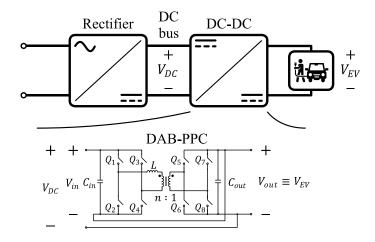

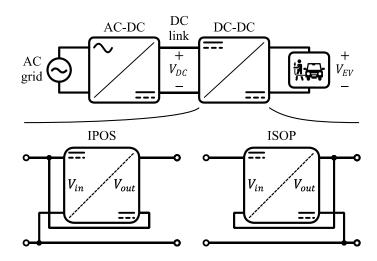

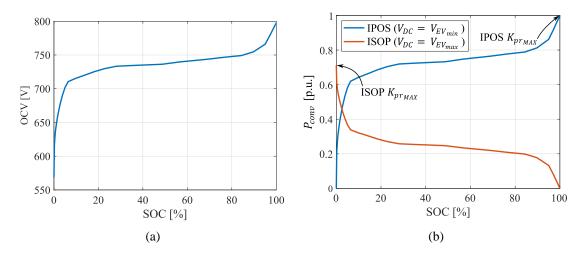

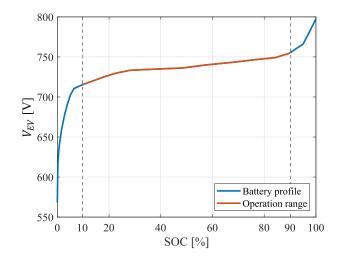

PPC architectures are divided into two groups: input-parallel-output-series (IPOS) or input-series-output-parallel (ISOP) type architectures, and fractional charging converters (FCC) type architectures. The main difference between the IPOS-ISOP type architectures and the FCC is the fact that the former requires isolated topologies. This thesis analyses the benefits that both type of architectures bring in comparison to conventional full power converter architectures. Simulations and experimental results conclude that IPOS-ISOP type architectures are the most promising solution in terms of volume reduction, high efficiency and low cost. Then, three applications of IPOS-ISOP type PPC architectures are studied for future implementation: electric vessel, hydrogen generation and electric vehicle (EV) fast charging.

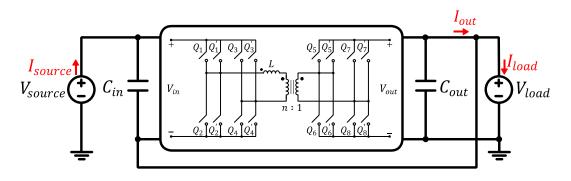

Finally, a 50 kW PPC is designed and validated for EV charging. The converter consists of a dual active bridge and, due to the PPC configuration, it processes a maximum power of 5 kW. This way, the implementation of Silicon-based discrete devices is enabled. The converter achieves a peak efficiency of 99.47 %.

## LABURPENA

Tesi honek DC-DC aplikazioetarako potentziaren prozesamendu partzialean (partial power processing, PPP) oinarritutako arkitekturak aztertzen ditu. Horrelako arkitekturen helburua potentzia-bihurgailuak prozesatutako potentzia murriztea da. Horrela, bihurgailuaren potentzia-galerak eta bolumena murrizten dira.

Lana PPP estrategiei buruzko ikuspegi orokor batekin hasten da. Alde horretatik, literaturan aurkitutako soluzioak hiru estrategia nagusitan sailkatzen dira: potentzia diferentzialeko bihurgailuak, potentzia partzialeko bihurgailuak (partial power converter PPC) eta estrategia mistoak. Bere aplikazio ugariengatik eta efizientzia handiko emaitzengatik, tesia PPC arkitekturetan zentratzen da.

PPC arkitekturak bi multzotan banatzen dira: sarrera-paralelo-irteera-seriea motako (input-parallel-output-series, IPOS) edo sarrera-serie-irteera-paraleloa (input-serieoutput-parallel, ISOP) motako arkitekturak, eta karga zatikatuko bihurgailu motako arkitekturak (fractional charging converter, FCC). IPOS-ISOP motako arkitekturen eta FCC arkitekturen arteko desberdintasun nagusia da lehenengoek topologia isolatuak behar dituztela. Tesi honetan, bi arkitektura motek potentzia osoko bihurgailuen arkitektura konbentzionalekin alderatuta ematen dituzten abantailak aztertzen dira. Simulazioen eta emaitza esperimentalen arabera, IPOS-ISOP motako arkitekturak dira irtenbiderik oparoena bolumen-murrizketari, efizientzia handiari eta kostu txikiari dagokienez. Ondoren, IPOS-ISOP motako PPC arkitekturen hiru aplikazio aztertzen dira, etorkizunean inplementatzeko: ontzi elektrikoa, hidrogenoa sortzea eta ibilgailu elektrikoen karga azkarra.

Azkenik, 50 kW-eko PPC bat diseinatu eta baliozkotzen da ibilgailu elektrikoa kargatzeko. Bihurgailua zubi aktibo bikoitz bat da eta, PPCaren konfigurazioa dela eta, 5 kW-ko potentzia maximoa prozesatzen du. Horrela, Silizion oinarritutako gailu diskretuak inplementatzeko aukera ematen da. Bihurgailuak % 99.47-ko gehieneko efizientzia lortzen du.

## RESUMEN

Esta tesis estudia las arquitecturas basadas en el procesamiento parcial de potencia (partial power processing, PPP) para aplicaciones DC-DC. Este tipo de soluciones tienen como objetivo reducir la potencia procesada por el convertidor de potencia. De este modo, se reducen las pérdidas de potencia y el volumen del convertidor.

El trabajo comienza con una revisión de las estrategias PPP. En este sentido, las diferentes soluciones encontradas en la literatura se clasifican en tres estrategias principales: convertidores de potencia diferencial, convertidores de potencia parcial (partial power converter, PPC) y estrategias mixtas. Debido a sus numerosas aplicaciones y a los resultados de alta eficiencia, la tesis se centra en las arquitecturas PPC.

Las arquitecturas PPC se dividen en dos grupos: arquitecturas del tipo entrada-seriesalida-series (input-parallel-output-series, IPOS) o entrada-serie-salida-paralelo (inputseries-output-parallel, ISOP), y arquitecturas de tipo convertidores de carga fraccionada (fractional charging converter, FCC). La principal diferencia entre las arquitecturas de tipo IPOS-ISOP y las FCC es el hecho de que las primeras requieren topologías aisladas. En esta tesis se analizan las ventajas que aportan ambos tipos de arquitecturas en comparación con las arquitecturas convencionales de convertidores de potencia completa. Las simulaciones y los resultados experimentales concluyen que las arquitecturas de tipo IPOS-ISOP son la solución más prometedora en términos de reducción de volumen, alta eficiencia y bajo coste. Después, se estudian tres aplicaciones de las arquitecturas PPC de tipo IPOS-ISOP para su futura implementación: buque eléctrico, generación de hidrógeno y carga rápida de vehículos eléctricos (VE).

Por último, se diseña y valida un PPC de 50 kW para la carga de VE. El convertidor consiste en un puente activo doble y, debido a la configuración del PPC, procesa una potencia máxima de 5 kW. De este modo, se permite la implementación de dispositivos discretos basados en Silicio. El convertidor alcanza una eficiencia máxima del 99.47 %.

## CONTENTS

| Chapter 1 | Introduction                                                     | .1  |

|-----------|------------------------------------------------------------------|-----|

| 1.1       | Background                                                       | . 2 |

| 1.2       | Overview of Power Converters                                     | . 5 |

| 1.3       | Efficiency Improvement Trends                                    | . 6 |

| 1.4       | Basis of Partial Power Processing                                | . 8 |

|           | 1.4.1 Concept Description                                        |     |

|           | 1.4.2 Applications of Partial Power Processing                   |     |

| 1.5       | Objectives and New Contributions of the Work                     | 14  |

| 1.6       | Chapter Overview                                                 | 17  |

| Chapter 2 | Partial Power Processing Overview                                | 19  |

| 2.1       | Partial Power Processing Based Architectures                     | 20  |

|           | 2.1.1 Differential Power Converter                               | 20  |

|           | 2.1.2 Partial Power Converters                                   | 25  |

|           | 2.1.3 Mixed Strategies                                           | 39  |

| 2.2       | Main Benefits and Drawbacks of Partial Power Processing          | 42  |

|           | 2.2.1 Benefits                                                   | 42  |

|           | 2.2.2 Drawbacks                                                  | 43  |

| 2.3       | Comparison Parameters                                            | 45  |

|           | 2.3.1 Processed Power by the Converter                           | 45  |

|           | 2.3.2 Electrical Stress of Components                            |     |

|           | 2.3.3 Thermal Stress: Top-Case Temperature of Semiconductors     |     |

|           | 2.3.4 Efficiency                                                 | 49  |

| Chapter 3 | Partial Power Converters That Do Not Require Isolated Topologies | 51  |

| 3.1       | Motivation, Investigated Topologies                              | 52  |

| 3.2       | Single Inductor Case Study.                                      |     |

|           | 3.2.1 Simulation Results                                         | 53  |

| 3.3       | Double Inductor Case Study                                       | 57  |

|           | 3.3.1 Simulation Results                                         | 59  |

| 3.4       | Experimental Results                                             | 60  |

|           | 3.4.1 Prototypes Design                                          | 60  |

|           | 3.4.2 Description of the Experimental Set-Up                     | 63  |

|           | 3.4.3 Experimental Results                                       | 64  |

| 3.5       | Conclusion                                                       | 67  |

| Chapter 4 | Partial Power Converters That Require Isolated Topologies        | 69  |

| 4.1       | Motivation, Investigated Topologies                              | 70  |

| 4.2       | IPOS-ISOP Type PPC vs. Non-Isolated Topology Based FPC           |     |

|           | 4.2.1 System Description                                         |     |

|           |                                                                  |     |

|      |       | 4.2.2 Power Converter Model                                  | 73   |

|------|-------|--------------------------------------------------------------|------|

|      |       | 4.2.3 Power Losses                                           | 79   |

|      |       | 4.2.4 Experimental Prototype                                 | 85   |

|      |       | 4.2.5 Simulation and Experimental Results                    | 88   |

|      |       | 4.2.6 Discussion                                             |      |

|      |       | 4.2.7 Conclusion                                             | .102 |

|      | 4.3   | Si-Based PPC vs SiC-Based FPC                                | .102 |

|      |       | 4.3.1 System Description                                     | .103 |

|      |       | 4.3.2 Analytical Modelling                                   | .106 |

|      |       | 4.3.3 Simulation and Experimental Results                    | .107 |

|      |       | 4.3.4 Discussion                                             | .116 |

|      |       | 4.3.5 Conclusion                                             | .117 |

| Chap | ter 5 | IPOS-ISOP architecture applications                          | .119 |

|      | 5.1   | Description                                                  | .120 |

|      | 5.2   | SEABAT                                                       |      |

|      |       | 5.2.1 System Description                                     |      |

|      |       | 5.2.2 Modular PPC Dimensioning                               |      |

|      | 5.3   | Hydrogen Generation                                          |      |

|      |       | 5.3.1 IPOS-ISOP Architecture Selection and Switching Devices |      |

|      | 5.4   | EV Fast Charging DC-DC.                                      |      |

|      |       | 5.4.1 System Description                                     |      |

|      |       | 5.4.2 Simulation Results                                     |      |

|      |       | 5.4.3 Experimental Results                                   |      |

|      |       | 5.4.4 Conclusion                                             |      |

| Chap | ter 6 | Design and Assembly of a High-Power PPC                      | .143 |

|      | 6.1   | Application Selection and Description                        | .144 |

|      | 6.2   | Prototype Design                                             |      |

|      |       | 6.2.1 Inductance                                             |      |

|      |       | 6.2.2 Switching Devices                                      |      |

|      |       | 6.2.3 Input-Output Capacitor                                 |      |

|      |       | 6.2.4 Heatsink and Thermal Interface                         | .156 |

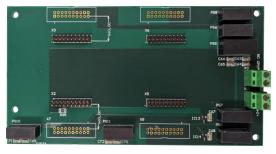

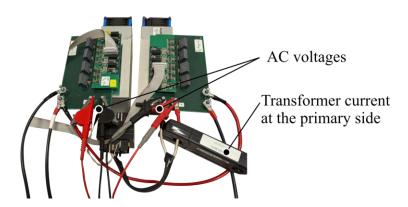

|      | 6.3   | Prototype Assembly                                           | .159 |

|      |       | 6.3.1 Transformer with Integrated Inductor                   |      |

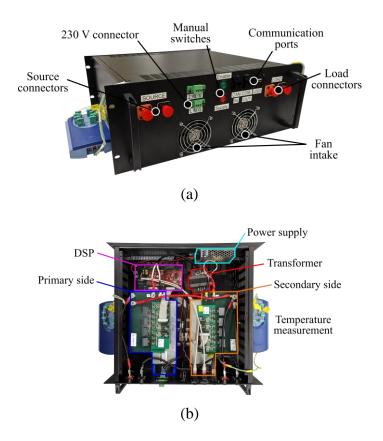

|      |       | 6.3.2 Rack assembly                                          | .161 |

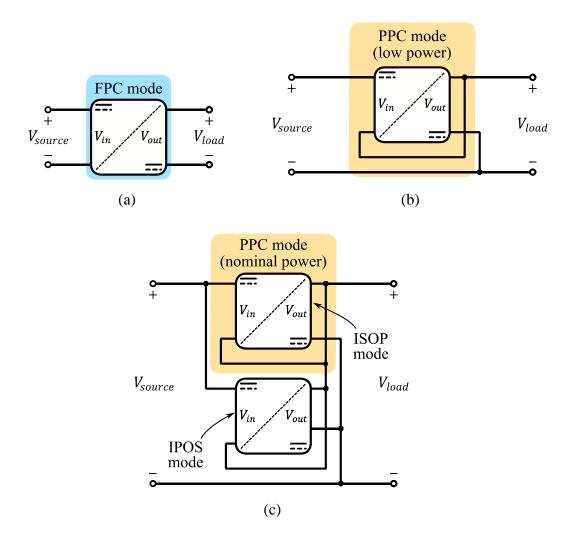

|      | 6.4   | Test Modes                                                   | .162 |

|      | 6.5   | Experimental Results                                         | .164 |

|      |       | 6.5.1 FPC Mode                                               | .165 |

|      |       | 6.5.2 PPC Mode at Low Power Conditions                       | .168 |

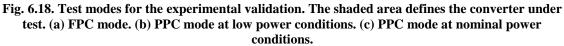

|      |       | 6.5.3 PPC Mode at Nominal Conditions                         | .169 |

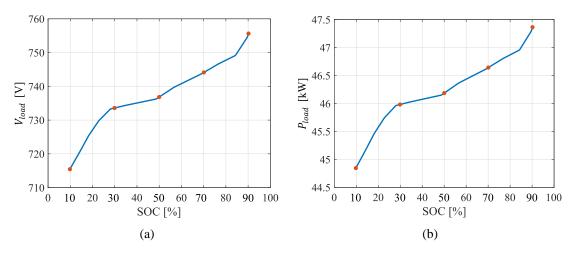

|      |       | 6.5.4 Extended Operation Range                               | .172 |

|      |       | 6.5.5 400 V EV Charging                                      | .175 |

|      | 6.6   | Discussion                                                   | .177 |

| Chap | ter 7 | Conclusions and Outlook                                      | .179 |

|      | 7.1   | Conclusions                                                  | .180 |

|      |       |                                                              |      |

| 7.2       | Outloo | ok                                         |  |

|-----------|--------|--------------------------------------------|--|

|           | 7.2.1  | FCC Type Architectures                     |  |

|           | 7.2.2  | IPOS-ISOP Type Architectures               |  |

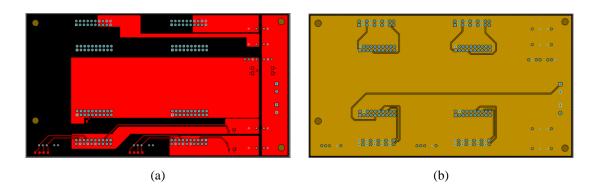

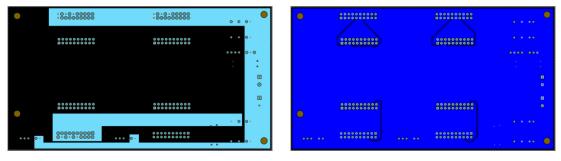

| Appendix  | A      | PCB Design of the High-Power PCB           |  |

| Appendix  | B      | Experimental results of the high power PPC |  |

| Reference | S      |                                            |  |

## GLOSSARY OF ABBREVIATIONS AND VARIABLES

#### Abbreviations

| AC    | Alternating current                              |

|-------|--------------------------------------------------|

| B2E   | Bus to element                                   |

| BOL   | Beginning of life                                |

| CAN   | Controller area network                          |

| CC    | Constant current                                 |

| CCM   | Continuous conduction mode                       |

| CCSF  | Capacitor component stress factor                |

| CSF   | Component stress factor                          |

| CSIFB | Current source isolated full bridge              |

| DAB   | Dual active bridge                               |

| DC    | Direct current                                   |

| DFIG  | Doubly-fed induction generator                   |

| DPC   | Differential power converter                     |

| E2E   | Element to element                               |

| EMI   | Electromagnetic interference                     |

| EOL   | End of life                                      |

| ESR   | Equivalent series resistance                     |

| ESS   | Energy storage system                            |

| EV    | Electric vehicle                                 |

| FCC   | Fractional charging converter                    |

| FPP   | Full power processing                            |

| FPC   | Full power converter                             |

| GaN   | Gallium nitride                                  |

| HB    | Half bridge                                      |

| HE    | High energy                                      |

| HESS  | Hybrid energy storage system                     |

| HP    | High power                                       |

| iZVS  | Incomplete zero voltage switching                |

| IEEE  | Institute of electrical and electronic engineers |

| IGBT  | Insulated-gate bipolar transistor                |

| IHB   | Interleaved half bridge                          |

| IMS   | Insulated metal substrate                        |

| IPOS   | Input-parallel-output-series                           |

|--------|--------------------------------------------------------|

| ISOP   | Input-series-output-parallel                           |

| LED    | Light emitting diode                                   |

| LFP    | Lithium-iron-phosphate                                 |

| LMO    | Lithium-manganese-oxide                                |

| MGEP   | Mondragon goi eskola politeknikoa                      |

| MOSFET | Metal-oxide-semiconductor field-effect-transistor      |

| MPPT   | Maximum power point tracking                           |

| MSIBC  | Modified switched inductor boost converter             |

| NaN    | Not a number                                           |

| NMC    | Nickel-manganese-cobalt                                |

| OBC    | On-board charger                                       |

| OCV    | Open-circuit voltage                                   |

| PCB    | Printed circuit board                                  |

| PPC    | Partial power converter                                |

| PPP    | Partial power processing                               |

| PSFB   | Phase shifted full bridge                              |

| PSM    | Phase shift modulation                                 |

| PV     | Photovoltaic                                           |

| RMS    | Root mean square                                       |

| SAE    | Society of automotive engineers                        |

| SCBU   | Series converter boost unit                            |

| SCSF   | Semiconductor component stress factor                  |

| SEABAT | Solutions for large batteries for waterborne transport |

| SOC    | State of charge                                        |

| SiC    | Silicon carbide                                        |

| TIM    | Thermal interface material                             |

| USB    | Universal serial bus                                   |

| VA     | Voltage-ampere                                         |

| WCSF   | Winding component stress factor                        |

| ZVS    | Zero voltage switching                                 |

|        |                                                        |

#### Symbols and variables

| A Area $[m^2]$ |  |

|----------------|--|

| A Area $[m^2]$ |  |

- C Capacitance [F]

- D Duty

- d Phase-shift

- *E* Energy [Wh]

| ESR    | Equivalent series resistance $[\Omega]$ |

|--------|-----------------------------------------|

| Ι      | Current [A]                             |

| L      | Inductance [H]                          |

| Ν      | Non-active power [VAr]                  |

| n      | Transformation ratio of the transformer |

| η      | Efficiency [%]                          |

| Р      | Active power [W]                        |

| Q      | Switching device                        |

| R      | Resistance [Ω]                          |

| t      | Time [s]                                |

| V      | Voltage [V]                             |

| $\phi$ | Phase-shift [deg]                       |

### Subscripts

| $C_{in}$                  | Input capacitor [F]                               |

|---------------------------|---------------------------------------------------|

| Cout                      | Output capacitor [F]                              |

| $E_{charged}$             | Energy charged [Wh]                               |

| Eloss                     | Energy losses [Wh]                                |

| E <sub>off</sub>          | Turn-off energy losses [Wh]                       |

| $E_{on}$                  | Turn-on energy losses [Wh]                        |

| Eoss                      | Output capacitance energy [J]                     |

| $f_{sw}$                  | Switching frequency [Hz]                          |

| $G_V$                     | Static voltage gain [p.u.]                        |

| I <sub>0</sub>            | Switching current [A]                             |

| I <sub>base</sub>         | Base current [A]                                  |

| I <sub>DC</sub>           | DC current [A]                                    |

| I <sub>in</sub>           | Converter input current [A]                       |

| $I_L$                     | Inductor current [A]                              |

| I <sub>load</sub>         | Load current [A]                                  |

| I <sub>out</sub>          | Converter output current [A]                      |

| I <sub>RMS</sub>          | RMS current [A]                                   |

| <i>I<sub>source</sub></i> | Source current [A]                                |

| k                         | Thermal conductivity [W/m·K]                      |

| $K_{pr}$                  | Partial power ratio                               |

| L <sub>lk</sub>           | Leakage inductance [H]                            |

| $n_{cell_m}$              | Number of series connected cells per module       |

| $n_s$                     | Number of series connected modules                |

| N <sub>C</sub>            | Non-active power processed by the capacitor [VAr] |

| N <sub>in</sub>     | Non-active power at the input terminals of the converter [VAr]  |

|---------------------|-----------------------------------------------------------------|

| N <sub>int</sub>    | Non-active power internally processed by the converter [VAr]    |

| $N_L$               | Non-active power processed by the inductor [VAr]                |

| N <sub>out</sub>    | Non-active power at the output terminals of the converter [VAr] |

| $N_p$               | Number of turns in the primary side winding                     |

| $N_s$               | Number of turns in the secondary side winding                   |

| N <sub>st</sub>     | Number of strands                                               |

| $N_t$               | Number of turns of an inductor                                  |

| N <sub>w</sub>      | Number of wires                                                 |

| $\eta_{sys}$        | System efficiency [%]                                           |

| $\eta_{conv}$       | Converter efficiency [%]                                        |

| P <sub>cond</sub>   | Conduction losses [W]                                           |

| $P_{cond}$          | Converter power [W]                                             |

| $P_E$               | Perimeter of EE type core [m]                                   |

| $P_{EV}^{L}$        | Electric vehicle power [W]                                      |

| $P_{in}$            | Converter input power [W]                                       |

| P <sub>load</sub>   | Load power [W]                                                  |

| $P_{loss}$          | Power losses [W]                                                |

| Poss                | Output capacitance power [W]                                    |

| $P_{out}$           | Converter output power [W]                                      |

| $P_{rr}$            | Reverse recovery power [W]                                      |

| P <sub>source</sub> | Source power [W]                                                |

| $P_{sw}$            | Switching losses [W]                                            |

| $P_{sys}$           | System power [W]                                                |

| $P_{VI}$            | Overlapping power [W]                                           |

| $Q_{oss}$           | Output capacitance charge [C]                                   |

| $Q_{rr}$            | Reverse recovery charge [C]                                     |

| $R_{CE}$            | Collector-emitter resistance $[\Omega]$                         |

| $R_{DS}$            | On-state resistance of a MOSFET $[\Omega]$                      |

| R <sub>SD</sub>     | Body diode resistance $[\Omega]$                                |

| $R_{th}$            | Thermal resistance [°C/W]                                       |

| t <sub>db</sub>     | Dead-band time [s]                                              |

| t <sub>fv</sub>     | Voltage falling time [s]                                        |

| t <sub>iZVS</sub>   | ZVS time [s]                                                    |

| t <sub>ri</sub>     | Current rising time [s]                                         |

| $T_{amb}$           | Ambient temperature [°C]                                        |

| $T_H$               | Heatsink temperature [°C]                                       |

| $T_j$               | Junction temperature [°C]                                       |

| $T_s$               | Period [s]                                                      |

|                     |                                                                 |

| $T_{ss}$            | Time-step [s]                            |

|---------------------|------------------------------------------|

| $V_0$               | Switching voltage [V]                    |

| V <sub>base</sub>   | Base voltage [V]                         |

| V <sub>bat</sub>    | Battery voltage [V]                      |

| $V_{CE_{sat}}$      | Collector-emitter saturation voltage [V] |

| $V_{CE_{test}}$     | Test voltage [V]                         |

| V <sub>cell</sub>   | Battery cell voltage [V]                 |

| $V_{DC}$            | DC voltage [V]                           |

| $V_{DS}$            | Drain to source voltage [V]              |

| $V_E$               | Series connected element voltage [V]     |

| $V_{EV}$            | Electric vehicle voltage [V]             |

| $V_F$               | Forward voltage of the diode [V]         |

| V <sub>in</sub>     | Converter input voltage [V]              |

| V <sub>load</sub>   | Load voltage [V]                         |

| $V_{mod}$           | Module voltage [V]                       |

| V <sub>out</sub>    | Converter output voltage [V]             |

| $V_{pk}$            | Peak voltage [V]                         |

| $V_{pl}$            | Plateau voltage [V]                      |

| V <sub>RMS</sub>    | RMS voltage [V]                          |

| V <sub>sd</sub>     | Source to drain voltage [V]              |

| V <sub>source</sub> | Source voltage [V]                       |

| $V_{th}$            | Thevenin voltage [V]                     |

|                     |                                          |

## Chapter 1

## INTRODUCTION

This Chapter introduces the research work with a brief description of the current energy transition plan and the role of power converters inside the electric system. Regarding power converters, these are classified according to its current/voltage waveforms and partial power processing is suggested for improving their efficiency and reducing their size. Together with this, the main concepts and terminology related to partial power processing are described. Finally, an overview of the most important applications where partial power processing strategies have potential benefits is carried out.

#### 1.1 Background

Nowadays, climate change is one of the main challenges for society. Proof of this is the statement issued by the Group of 20 (G20) during the G20 summit in Rome [1]. For the first time, the leaders acknowledged officially that its members' emissions reduction plans needed to be firmed up over this decade to put them on track for net zero by 2050.

In order to achieve this objective, the document states necessary to design an energy transition plan towards to sustainable energy. This implies radical structural changes in today's energy system, for example: distributed generation, transition to renewable energy and more electric transportation (train, aircraft or electric vehicle, EV). Renewables are expected to account for 90 % of total global power capacity increases in 2022 [2] and the emergence of the EV through the last 3 years is unquestionable [3]. Still, it is important to highlight the importance of public administrations to promote renewable energy production and develop energy efficiency plans.

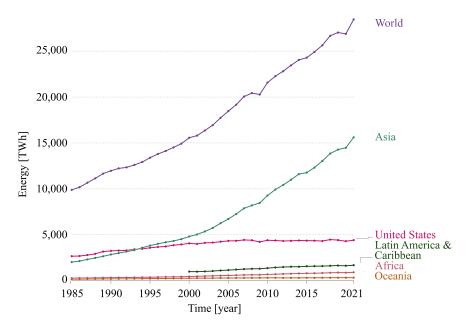

Regarding energy efficiency, this can be defined as the reduction of the amount of energy required to provide products and services. It is estimated that the consumed energy only consists of a 33 % of the total energy produced [5], which means that more energy is wasted than used. Over the last 40 years, massive generation and consumption points have been built to meet society's energy needs. Fig. 1.1 shows the increment of the

Fig. 1.1. Electricity generation evolution since 1985 [4].

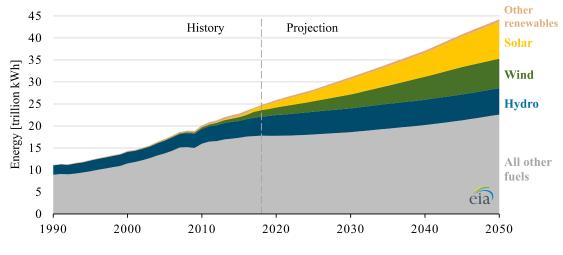

electricity generation since 1985. As it can be observed, the world energy generation is constantly growing, especially due to the Asian continent. Inside the energy generation, renewables sources are gaining more importance. Indeed, in 2018, renewable sources produced the 28 % of global electricity, and they will provide 49 % by 2050 (Fig. 1.2).

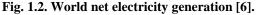

On the other hand, there also exist large consumption points, such as, EV fast charging stations (few MW [7]) and data centers (hundreds of MW [8], [9]). Due to its efficient performance and reduced green-house emissions, the EV is turning into a real alternative to conventional combustion based vehicles. Authors from [10] expect a total charging energy demand increment from roughly 20 billion kWh to about 280 billion kWh for 2030 (Fig. 1.3a). Regarding data centers, they accounted for 1.1 % to 1.5 % of worldwide electricity consumption in 2010 [11] and they will use around 3 % to 13 % of global electricity in 2030 [12] (Fig. 1.3b). Considering all this, energy efficiency has turned into a great concern when it comes to the installation of these massive facilities. A slight efficiency improvement of 1 % in any of them can lead to a reduction in power losses of tens of MW.

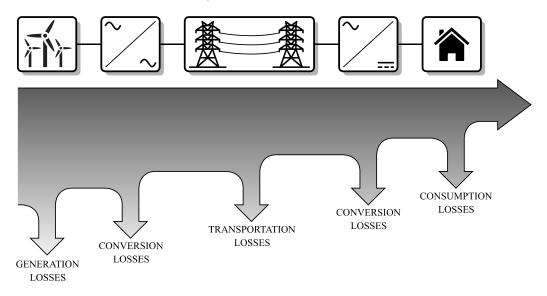

From its production to its consumption, the electrical energy is transported and converted several times (Fig. 1.4). In each of these steps, a certain amount of power losses is produced: generation losses, conversion losses, transportation losses and consumption losses. Focusing on the conversion losses, these are related to the energy transformations performed by a combination of passive (power transformers) and active (power converters) devices. The aim of both is to transfer electric power between two points with

Fig. 1.3. Large consumption applications usage. (a) Expected EV energy demand for 2025 and 2030 [10]. (b) Global electricity demand of data centers from 2010 to 2030 [12].

**Fig. 1.4. Simplified single-wire diagram of the electric power distribution and its main power losses.** different voltage levels or waveforms. Therefore, their application extends to the entire electric grid: power drives, electronic devices supply, home appliance... Bearing this in mind, power converters are considered as a key component whose performance and efficiency must be improved for achieving a sustainable future.

#### **1.2 Overview of Power Converters**

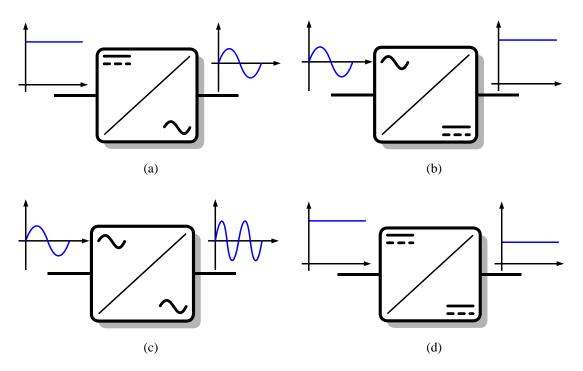

There exist many different criteria to classify power converters: number of components, galvanic isolation, current/voltage source... But, when it comes to the current's waveform, there exist 3 types of power converters: (i) DC-AC or AC-DC, (ii) AC-AC and (iii) DC-DC.

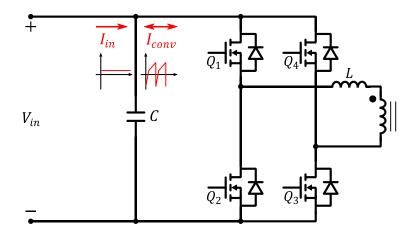

First, a DC-AC (power inverter, Fig. 1.5a) or an AC-DC (power rectifier, Fig. 1.5b) is implemented on applications where it is required to change from direct current to alternating current or vice versa. Inverters have as input a constant voltage or current and by switching a series of semiconductors, they are capable of generating at the output an AC signal. Rectifiers aim to transform a periodically reversing current into a unidirectional flow.

Second, there are the AC-AC converters, which convert a source of alternating current from one voltage level and/or frequency to another (Fig. 1.5c). The simplest example is the power transformer, which can be considered as a passive AC-AC converter capable of elevating or reducing the voltage. Also, there exist AC-AC solutions were a rectifier and an inverter are connected in series with a DC bus in between.

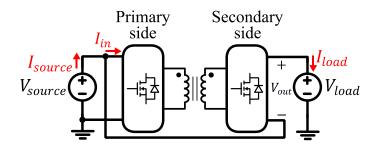

Fig. 1.5. Simplified single-wire diagram of a (a) DC-AC. (b) AC-DC. (c) AC-AC. (d) DC-DC.

Finally, there are the DC-DC converters, which transform a source of direct current from one voltage level to another (Fig. 1.5d). Similar to AC-AC converters, a DC-DC can be compound by an inverter and a rectifier with a high frequency transformer in between. This type of solutions are known as isolated topologies and they provide galvanic isolation to the system where they are applied. The galvanic isolation refers to the fact that the output and input power circuits are electrically and physically isolated between them [13]. This can be effective to prevent from current flow between two circuits with different potential.

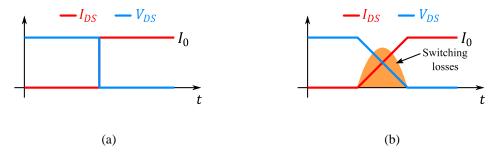

#### **1.3 Efficiency Improvement Trends**

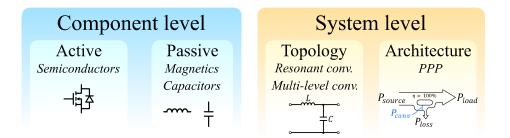

Power conversion is considered as a key sector inside the energy transition and, hence, great efforts are being made to improve the performance of power converters. These are divided in two main groups: component level and system level (Fig. 1.6). Inside the component level, improvements related to specific devices are included. These devices can be active or passive. On the other hand, the system level comprehends advanced or novel converter topologies and architectures.

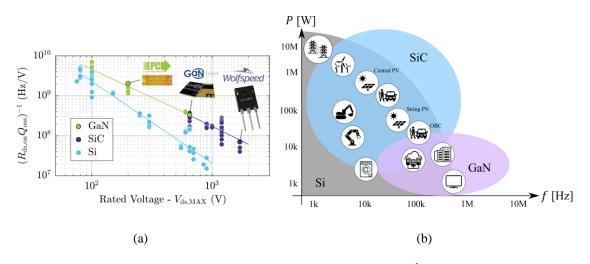

Regarding active components, there is the transition towards wide-bandgap (WBG) semiconductors. Higher energy efficiency and reduced power converter size are the main benefits that WBG devices present against conventional Silicon (Si) based semiconductors [14], [15]. Furthermore, these WBG semiconductors permit devices to operate at much higher voltages and temperatures (typical application of Silicon Carbide, SiC), and higher frequencies (typical application of Gallium Nitride, GaN) than the conventional Si semiconductors [16]. Apart from that, WBG semiconductors offer a better performance in terms of conduction and switching losses. Fig. 1.7a compares the

Fig. 1.6. Block diagram of the main efficiency improvement trends.

Fig. 1.7. Comparison between Si and WBG devices. (a)  $FoM = \frac{1}{R_{DS} \cdot Q_{oss}}$  for the majority of commercially available Si, SiC and GaN [19]. (b) Applications [20].

on-state resistance ( $R_{DS}$ , representative for conduction losses) and the charge stored in the transistor's output capacitance ( $Q_{oss}$ , representative for switching losses). As it can be observed, WBG semiconductors clearly outperform Si devices. Consequently, solar, traction, and EV applications are already implementing power converters with WBG based devices [17]. Fig. 1.7b shows the typical applications of Si and WBG semiconductors.

However, semiconductors' progress is not enough when high power density converters are required. The passive components and the cooling system inside the power converter are limiting the performance [18]. Therefore, the design of the magnetics and the capacitors has turned into an important topic to put the effort on.

System level wise, a research trend that aims to enhance the characteristics of power converters is the design of high efficient topologies. An example of this are resonant tanks that seek soft-switching conditions of the semiconductors [21], [22], and multi-level topologies that reduce the final cost of the converter by using lower voltage class devices [23], [24]. Last but not least, over the last decade, novel power delivery architectures based on partial power processing (PPP) have been presented. This type of architectures aim to reduce the power to be processed by the converter and they are considered as attractive solutions regarding power converter downsizing and efficiency improvement.

### 1.4 Basis of Partial Power Processing

#### **1.4.1 Concept Description**

The PPP concept was presented for the first time in spacecraft industry [25], where downsizing power converters connected to photovoltaic (PV) panels was the main priority. This way, a more efficient converter with higher power density was achieved without affecting the robustness of the system. As time passed by, this same concept was developed for further renewables applications based on wind generation [26], energy storage system (ESS) [27] and EV fast charging applications [28].

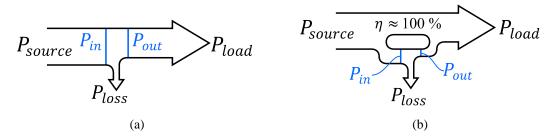

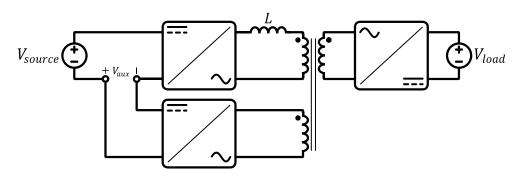

A power converter based on the PPP concept only processes a reduced percentage of the total power that goes from the source to the load. As example, Fig. 1.8 compares the power flow of a Full Power Processing (FPP) based converter and PPP-based converter. The FPP-based converter (Fig. 1.8a) is designed to process the 100 % of the power that flows from the source to the load. On the other hand, Fig. 1.8b shows the PPP concept, which is based on achieving a reduction of the power processed by the converter. In other words, the PPP-based converter processes only a fraction of the power that flows from the source to the load. This way, it is expected to implement lower rated components, reduce the power losses and achieve a smaller solution.

In the FPP case, since the system power and the converter power are the same, it is concluded that the efficiency of the system  $(\eta_{sys})$  and the efficiency of the converter  $(\eta_{conv})$  are identical (1.1). On the other hand, a PPP-based converter processes a reduced amount of the system power, thus their efficiencies must be treated as different parameters. However, they will be related by the processed power ratio of the converter

Fig. 1.8. Power flow diagram. (a) FPP. (b) PPP.

| Parameter                                                       | Meaning                                       |

|-----------------------------------------------------------------|-----------------------------------------------|

| $V_{in}, I_{in}, P_{in}$                                        | Input voltage/current/power of the converter  |

| $V_{out}, I_{out}, P_{out}$                                     | Output voltage/current/power of the converter |

| V <sub>source</sub> , I <sub>source</sub> , P <sub>source</sub> | Source voltage/current/power                  |

| $V_{load}, I_{load}, P_{load}$                                  | Load voltage/current/power                    |

| $\eta_{conv}, \eta_{sys}$                                       | Converter/system efficiency                   |

Table 1.1. Definition of the main electrical parameters of an electric circuit.

$(K_{pr})$ , which consists of the division between the converter power and the system power (1.2). The term  $K_{pr}$  will be further explained in detail.

$$\eta_{sys_{FPP}} = \frac{P_{load}}{P_{source}} = \eta_{conv} = \frac{P_{out}}{P_{in}}$$

(1.1)

$$\eta_{sys_{PPP}} = \frac{P_{load}}{P_{source}} = 1 - \frac{P_{in}}{P_{source}} \cdot (1 - \eta_{conv}) = 1 - K_{pr} \cdot (1 - \eta_{conv})$$

(1.2)

As shown in equation (1.2), in the PPP case, it is important to differentiate the voltage, current or power characteristics of the converter and the system. Therefore, with the aim of clarifying the difference between the performance of a power converter and the performance of the whole system, Table 1.1 describes the main electrical parameters and their corresponding naming. Through the rest of the document, the terms input and output will refer to the converter. The terms source and load will refer to the system.

#### 1.4.2 Applications of Partial Power Processing

Through the last decade, PPP based architectures have been presented as promising solutions to many different types of applications.

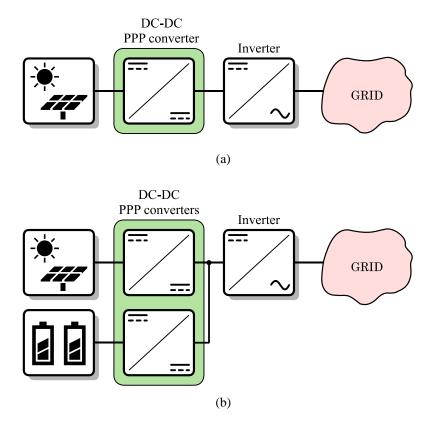

In the first place, there are the renewable sources applications such as, photovoltaic (PV) generation (Fig. 1.9a). In order to inject into the electrical grid the energy generated by the PV modules, two different power converters are required: a DC-DC and a DC-AC. The first one is in charge of implementing the maximum power point tracking (MPPT) at the PV module and keeping a constant voltage level of the DC bus between both converters. The second one injects to the electrical grid the produced energy at a correct phase. Authors from [29]–[31] present different PPP solutions that focus on the design of the DC-DC converter.

Fig. 1.9. Simplified single-wire diagram of a PV application. (a) Simple. (b) Supported with an ESS.

Related to the previous application, due to the fluctuation of PV generation, the final solution usually requires an ESS to fit the energy production and the consumption profiles (Fig. 1.9b). Actually, ESSs are considered as a key tool for achieving a flexible European power system through its transition to net zero emissions [32]. Therefore, the development of new technologies that can improve the performance of this type of applications are highly requested, for example, PPP based converters. Due to the fact that an ESS suffers both, charging and discharging processes, the concerned DC-DC converter must be capable of handling a bidirectional power flow. Through the literature, several examples with bidirectional PPP strategies can be found [27], [33].

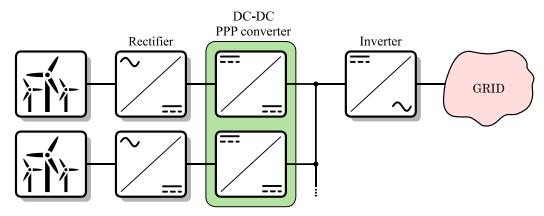

Another interesting application of PPP inside renewable energies is its implementation on wind generation. For example, authors from [34], [35] suggest PPP based converters for a DC collection system (Fig. 1.10). In this case, it consists of a series of DC-DC converters that connect to the same DC bus. Then, a single or various inverters inject the generated energy into the grid.

Fig. 1.10. Simplified single-wire diagram of a wind farm application.

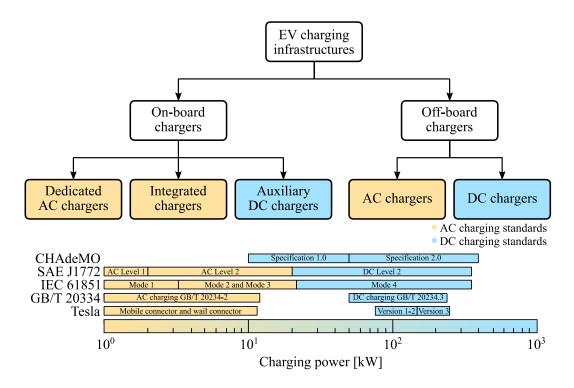

Another sector that is showing great interest on the development of PPP based architectures is the one of the EV. Indeed, due to its efficient performance and reduced green-house emissions, the EV is turning into a real alternative to conventional combustion based vehicles. However, EVs' main disadvantage is their low autonomy, which can reach up to 550 km [36]. In addition, the lack of charging infrastructure can lead to driving range anxiety [37]. Therefore, in order to avoid this, an extensive and solid EV charging stations grid is required.

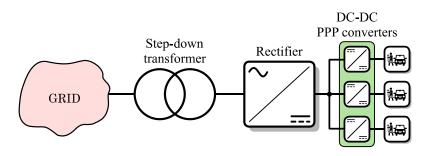

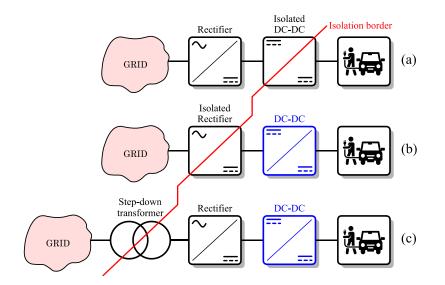

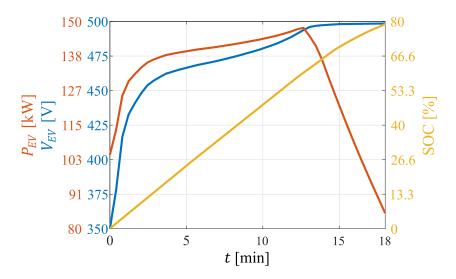

When it comes to the installation of the charging stations, one can find different types of solutions divided by their power level. On the one hand, up to 10 kW AC charging stations can be found. Usually, this type of charging structures are located where people spend great part of the day, for example: at home or at work. On the other hand, DC wise, two main groups exist: fast charging stations (between 20 kW and 120 kW) and extreme fast charging stations (higher than 120 kW). Due to the high peak power values, the charging times can be reduced up to 15 minutes, which makes the EV more attractive to the customer. Regarding fast charging stations, they are structures that are divided in different phases [38] (Fig. 1.11). Usually, fast charging stations are connected to a medium voltage AC grid and, then, the voltage level is reduced and rectified. Finally, several DC-DC power converters are implemented to charge each EV at the station. Concerning the DC-DC converter, several authors from the literature suggest to implement PPP based converters [28], [39], [40].

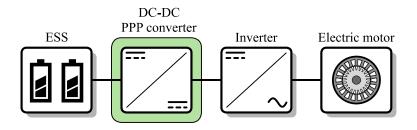

Another application of PPP inside the EV is the power drive, which is located between the ESS and the inverter connected to the motor (Fig. 1.12). In this case, since it

Fig. 1.11. Simplified single-wire diagram of EV fast charging station.

exists a power flow towards and from the ESS (acceleration or brake), the concerned converter must be bidirectional. At present, there are not publications that propose or mention specific PPP solutions for this type of applications. But, regarding the benefits that PPP offers (reduced sized converter and lower rated components), it is obvious that this type of technology suits very well in an EV's power drive application.

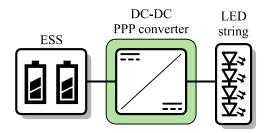

Apart from the power drive of the EV, PPP architectures can also be applied for supplying the car headlights (Fig. 1.13.) The great majority of the headlights implemented on vehicles are based on light emitting diodes (LED) technology. Through the literature, there can be found examples of PPP solutions for LED current balancing. Authors from [41] comment that the voltage-current characteristic of the LEDs is not always the same, specially when a failure occurs. Therefore, when LED strings are connected in parallel, the illumination is not uniform if the same voltage is applied to all strings. In consequence,

Fig. 1.12. Simplified single-wire diagram of the power drive of an EV.

Fig. 1.13. Simplified single-wire diagram of a LED string supply.

Fig. 1.14. Simplified electric circuit of a current balancing application.

PPP architectures are implemented to correct the concerned unbalance with reduced processed power.

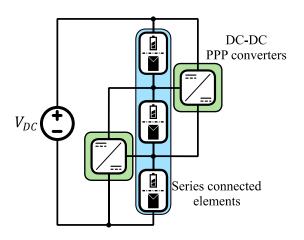

Additionally, authors from [42]–[45] propose PPP techniques for current balancing purposes of series connected elements, for example: PV modules or individual cells inside a whole energy storage pack (Fig. 1.14). The main objective of this type of solutions is to optimize the individual performance of an element inside a series string. In order to achieve it, these current diverters are designed to process the mentioned imbalance, and not the total power consumed/supplied by the sum of the elements.

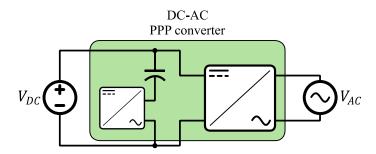

Until this point, only DC-DC converters have been considered as possible PPP applications. However, there also exists literature around power inverters that are based on PPP strategies [46]–[48]. Some of these solutions were motivated by Google's "little box challenge" [49], which was launched together with the Institute of Electrical and Electronic Engineers (IEEE) in 2014. The challenge required to build a power inverter that was about one-tenth the size of the state of the art at the time (6.5 dm<sup>3</sup>). In addition, it had to have an efficiency greater than 95 % and handle loads of 2 kW. This lead to multiple strategies, in which PPP was one of them. As example, Fig. 1.15 presents a high-level schematic of the proposed solution in [46]. There, a "buffer architecture is proposed for power pulsation decoupling in power conversion between DC and single phase AC".

In conclusion, the literature proves that PPP strategies offer a wide variety of applications.

Fig. 1.15. Simplified electric circuit of a PPP based DC-AC application.

# 1.5 Objectives and New Contributions of the Work

The main objective of this work is to improve the performance of the DC-DC converter through PPP. Bearing this in mind, the sub-objectives are set to:

- Tackle the challenges and drawbacks of PPP-based converters.

- Demonstrate the benefits that PPP-based converters bring compared to conventional FPP solutions.

The new contributions of this work are:

- Review of the PPP literature and classification of the different strategies.

- Demystifying the application of DC-DC non-isolated topologies on partial power architectures.

- Demonstrate that the Si-based PPP converter has improved performance than SiCbased FPP converter in all metrics: thermal stress, efficiency, volume and cost.

- Design and assembly of a 50 kW DC-DC converter based on PPP.

Different parts of this thesis including texts, tables, figures and equations have been previously published in scientific international journals and conference proceedings. The publications are listed in the following:

### **Conference** papers

[C1] J. Anzola, I. Aizpuru, and A. Arruti, "*Non-Isolated Partial Power Converter for Electric Vehicle Fast Charging Stations*," 2020 IEEE 11th International Symposium on Power Electronics for Distributed Generation Systems (PEDG) 2020.

[C2] J. Anzola et al., "Partial power processing based charging unit for electric vehicle extreme fast charging stations," 2020 IEEE Vehicle Power Propulsion Conference (VPPC) 2020.

**[C3]** J. Anzola et al., "*Resonant Dual Active Bridge Partial Power Converter for Electric Vehicle Fast Charging Stations*," 2021 IEEE Vehicle Power and Propulsion Conference (VPPC) 2021.

[C4] J. Anzola, S. Sharma, I. Aizpuru, and S. Bhattacharya, "Silicon Application *Extension Versus WBG Due to Partial Power Processing*," 2022 IEEE Applied Power Electronics Conference (APEC) 2022.

**[C5]** J. S. Artal-Sevil, C. Bernal-Ruiz, J. Anzola, I. Aizpuru, A. Bono-Nuez, and J. M. Sanz-Alcaine, "*Partial power processing architecture applied to a battery energy storage system*," 2020 IEEE Vehicle Power Propulsion Conference (VPPC) 2020.

**[C6]** J. S. Artal-Sevil, V. Ballestín-Bernard, J. Anzola, and J.A. Domínguez-Navarro, *"High-Gain Non-isolated DC-DC Partial-Power Converter for Automotive Applications,"* 2021 IEEE Vehicle Power Propulsion Conference (VPPC) 2021.

**[C7]** J. S. Artal-Sevil, J. Anzola, V. Ballestín-Bernad, and J.L. Bernal-Agustín, "*Analysis and Implementation of different non-isolated Partial-Power Processing Architectures based on the Cuk Converter*," 2022 24th European Conference on Power Electronics and Applications (EPE'22 ECCE Europe) 2022.

**[C8]** J. S. Artal-Sevil, J. Anzola, V. Ballestín-Bernad, and I. Aizpuru, "*Bidirectional Cuk Converter in Partial-Power Architecture with Current Mode Control for Battery Energy Storage System in Electric Vehicles*," 2022 24th European Conference on Power Electronics and Applications (EPE'22 ECCE Europe) 2022.

Other contributions out of the thesis:

**[C9]** J. Anzola, I. Aizpuru, and A. Arruti, "Development of an Algorithm for the Automation of the Modelling Process of Power Converters," 2020 22nd European Conference on Power Electronics (EPE'20 ECCE Europe) 2020.

[C10] A. Aizpuru, A. Arruti, J. Anzola, U. Iraola, M. Mazuela, and A. Rujas, "Universal electric vehicle charging infrastructure analysis tool," 2020 IEEE Vehicle Power Propulsion Conference (VPPC) 2020.

[C11] A. Arruti, F. J. Perez-Cebolla. J. Anzola, I. Aizpuru, and M. Mazuela, "Analytical, *FEM and Experimental Study of the Influence of the Airgap Size in Different Types of Ferrite Cores*," 2022 24nd European Conference on Power Electronics (EPE'20 ECCE Europe) 2022.

### Journal papers

[J1] J. Anzola et al., "Review of Architectures Based on Partial Power Processing for DC-DC Applications," IEEE Access, vol. 8, pp. 103405–103418, 2020.

[J2] J. Anzola, I. Aizpuru, and A. Arruti, "*Partial power processing based converter for electric vehicle fast charging stations*," Electronics, vol. 10, no. 3, pp. 1–17, 2021.

[J3] J. Anzola, I. Aizpuru, A. Arruti, J. S. Artal-Sevil, and C. Bernal-Ruiz, "*Demystifying non-isolated DC-DC topologies on partial power processing architectures*," Electronics, vol. 11, no. 3, p. 480, 2022.

[J4] J. Anzola, S. Sharma, I. Aizpuru, S. Bhattacharya, J. S. Artal-Sevil, "*Performance Improvement of a Silicon Partial Power Converter over a Silicon Carbide Full Power Converter*" Under revision in Transactions on Transportation Electrification

[J5] J. Anzola, E. Garayalde, J. Urkizu, A. Alacano, R. Lopez-erauskin, "*High Efficiency Converters based on Modular Partial Power Processing for Fully Electric Maritime Applications*" Under revision in Energy Reports

# **1.6 Chapter Overview**

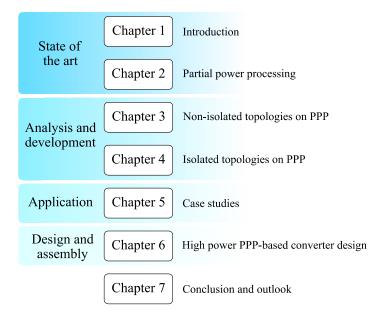

Fig. 1.16 describes the structure of the thesis, gathering the different Chapters according to the part of the work they represent:

**Chapter 1** introduces power converters by describing their role inside the electric grid, the different types that exist and advanced solutions that improve their performance. One of the suggested solutions is PPP, which is the main topic of this document.

**Chapter 2** reviews the literature on PPP, classifies the different strategies according to their characteristics and explains their working principles. Then, their main drawbacks and challenges are detailed. At the end of the Chapter, the comparison parameters that are considered for converters analysis are defined.

**Chapter 3** discusses the possibility of achieving partial power processing with nonisolated DC-DC topologies. The results from simulations and experimental tests conclude that single inductor non-isolated topologies cannot achieve partial power processing. However, double inductor non-isolated topology can improve its efficiency with PPPbased architectures.

Fig. 1.16. Structure of the thesis Chapters.

**Chapter 4** compares the performance of a conventional FPP-based and a PPPbased converter. The comparison focuses on the switching mode of the devices, their thermal stress and the system efficiency.

**Chapter 5** presents three different applications where PPP-based converters are considered for implementation: electric vessel, hydrogen generation and EV charging. Each case study analyses the benefits of the PPP solution and it describes its design steps.

**Chapter 6** describes the steps followed to design and assemble a 50 kW DC-DC PPP-based converter. Due to the reduced converter power, the prototype is enabled with discrete devices and efficiencies above 99 % are achieved.

Chapter 7 defines the main conclusions reached in this research project.

# Chapter 2

# PARTIAL POWER PROCESSING OVERVIEW

This Chapter gives an overview of the most repeated PPP strategies in the literature. With this purpose, three main strategies are identified and classified according to their characteristics: differential power converters, partial power converters (PPC) and mixed strategies. Especial interest is shown to PPCs due to their diverse literature and numerous applications. Together with this, the main disadvantages and challenges that PPP strategies present are detailed and discussed.

Finally, different factors that affect the behaviour of the converter and which will be used for converters comparison are presented.

Significant content from this Chapter corresponds to the journal article [J1].

# 2.1 Partial Power Processing Based Architectures

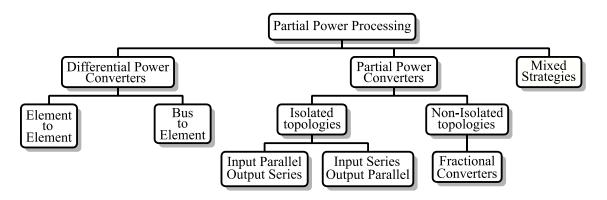

Although the first steps taken on the PPP area were in the 1990s [25], [50], the interest in this type of architectures did not began until 10 years ago. For this reason, the recent literature around PPP presents a confusing nomenclature. Indeed, identical architectures receive different names and, vice versa, the same name is used to refer to different architectures. Therefore, with the aim of setting a universal naming criteria, the present Chapter proposes to differentiate 3 main PPP strategies (Fig. 2.1):

- *Differential Power Converters (DPC):* they consist of active balancing circuits that aim to optimize the individual performance in series-connected DC voltage domains.

- *Partial power converters (PPC):* their main goal is to control the power flow between a source and a load with different voltage level.

- *Mixed strategies:* they offer a better performance at specific applications where DPC and PPC converters present considerable disadvantages.

# 2.1.1 Differential Power Converter

The architectures based on the DPC concept are well defined in [42] as power converters that aim to correct current imbalances that exist between different elements connected in series to the same voltage bus. In consequence, instead of processing the total power consumed/supplied by the sum of the elements, this type of converters only process the mismatch by providing the difference between the elements' current. DPCs

Fig. 2.1. Overview of PPP strategies.

were presented in [50]–[52] for ESS applications as a "new technique for equalizing a series battery stack". There, different active balancing solutions are proposed, such as, parallel connected Flyback modules and buck-boost current diverters. Later, the same architectures are further developed in [43], [53]–[56] by implementing improved topologies, for example: a buck-boost with shared-core inductors and a dual active bridge (DAB). In consequence, the implementation of this type of architectures is extended to PV applications with current balancing purposes [44], [45], [57]–[59] and more efficient DC power distribution of data centers [56]. The research from [60] is recommended for extended information around DPC architectures, specifically, Sections 4 and 5.

Inside the literature around DPCs, there is a considerable confusion in their naming. In the first place, authors from [51], [53] introduce the term "equalizer" or "battery system equalizer" to refer to an active balancing circuit. However, years after, authors from [44], [58], [59] started to use the terms DPC and "current diverter converter", and in [45], [57] the term "parallel-connected PPC" is used to refer to the same current balancing solution. Also, authors from [43], [54]–[56] use a different term to refer to the same architecture: "returned energy architecture", "Parallel connected submodule integrated converter", "input series output parallel" and DPC.

As it can be observed, within the active balancing literature, there is a lack of agreement on the naming criteria. Therefore, this document proposes to use the term DPC to refer to a power converter that has current balancing purposes.

Depending on the energy flow strategy, DPC architectures are divided into 2 main groups:

- 1. *Element to Element (E2E):* the energy is transferred between neighbouring elements.

- 2. *Bus to Element (B2E):* the energy is transferred from a common bus to each individual element and/or vice versa.

### **Element to element**

In order to optimize the performance of individual series connected elements, E2E type architectures are focused on transferring the energy between neighbour elements

Fig. 2.2. E2E type DPC architecture with a single inductor HB topology.

[43]–[45], [51], [53], [57], [58], [61]. To explain this, Fig. 2.2, presents the current and power flows by red and blue arrows, respectively. The power delivered by the source is divided by the number of elements (*n*). However, the power processed by each converter is given by the current that flows through the inductor  $(I_{L_i})$ , which depends on the currents of the neighbouring elements.

The main advantages of E2E architectures are the number of necessary converters (n-1 converters for n elements) and the fact that the devices are designed for lower voltage and current values. Nevertheless, the switching states of the converters are not independent and the DC link voltage  $(V_{DC})$  is the result of the sum of the elements connected in series. Therefore, if the application requires to raise or reduce this voltage, an additional converter would be necessary.

Focusing on Fig. 2.2, it can be seen that each power converter consists of a conventional single inductor half-bridge (HB). The total power processed by the converters ( $P_{E2E}$ ) is the sum of the power processed by each one (2.1).

$$P_{E2E} = \sum_{i=1}^{n-1} V_{E_i} \cdot |I_{L_i}|$$

(2.1)

Where  $V_{E_i}$  is the average element voltage of the  $i^{th}$  converter and  $I_{L_i}$  is the average inductor current of the  $i^{th}$  converter.

On the other hand, by applying Kirchhoff's current law to the intermediate nodes between the series connected elements, the average inductor current value of each converter is obtained (2.2). As it can be observed, the average inductance current inside the converter depends on the currents of the adjacent elements.

$$I_{L_i} = I_{E_i} - I_{E_{i+1}} + D_{i-1} \cdot I_{L_{i-1}} + (1 - D_{i+1}) \cdot I_{L_{i+1}}$$

(2.2)

Where,  $I_{E_i}$  is the current of the  $i^{th}$  element and  $D_i$  is the duty ratio of the high side switch of the  $i^{th}$  converter.

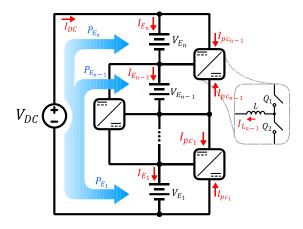

#### Bus to element

B2E type architectures (Fig. 2.3) are aimed to transfer energy between an element in series and the common bus [50], [52], [54]–[56], [62]–[64]. This common bus can be a virtual bus voltage (represented as  $C_{bus}$  in Fig. 2.3a) or the same input/output bus (represented as  $V_{DC}$  in Fig. 2.3b). The main purpose of the common bus is to compensate an instantaneous power mismatch by injecting or rejecting current to the series connected elements. Compared to E2E architectures, B2E type offers greater modularity and independence between converters. However, a higher number of converters is required (*n* converters for *n* elements) and the components are designed for higher voltage and

Fig. 2.3. B2E architecture with bidirectional Flyback topology. (a) Virtual bus. (b) Common bus.

current values [42], [44]. As E2E type architectures, in case it is desired to regulate the value of  $V_{DC}$ , B2E architectures also require an additional converter.

Regarding the converters' topology from Fig. 2.3, it is observed that an isolated topology is necessary to avoid a string short-circuit. In this case, a bidirectional Flyback converter is shown as example. The total power processed by the sum of each converter is given by equation (2.3).

$$P_{B2E} = \sum_{i=1}^{n} V_{E_i} \cdot |I_{DC_i}|$$

(2.3)

Finally, equation (2.4) shows the current that each converter must process.

$$I_{DC,i} = I_i - I_{i+1} + I_{DC,i+1}$$

(2.4)

#### Overview

With the aim of resuming the main results extracted from the DPC literature, Table 2.1 points out the key characteristics of the main articles. Since each prototype is tested under different conditions, the aim of Table 2.1 is not to compare the obtained results by each reference, but to make the reader see the goals achieved by each converter presented in the literature (together with their corresponding solutions and applications).

At first glance, it can be observed that there is no predominant architecture, both, E2E and B2E are implemented equally. However, it is clear that the main application of this type of solutions is the PV, followed by state of charge (SOC) balancing. Regarding the topologies of the converters, the most popular topology in E2E architectures is the single inductor HB and, in B2E, the Flyback. When it comes to the  $K_{pr}$ , the first references around this type of architecture do not specify this value, since it was not their main objective. The rest of the articles present  $K_{pr}$  values that go from 0 % to 66 %. This value depends on the mismatch to correct.

| Ref.              | Architectures | K <sub>pr</sub> | $\eta_{sys}$ | Topology                        | Application   |

|-------------------|---------------|-----------------|--------------|---------------------------------|---------------|

| [50]              | B2E           | -               | -            | Flyback                         | ESS balancing |

| [51]              | E2E           | -               | -            | Single inductor HB              | ESS balancing |

| [52]              | B2E           | -               | -            | Multi input Flyback             | ESS balancing |

| [53]              | E2E           | -               | -            | Buck-Boost                      | ESS balancing |

| [55]              | B2E           | From 0 to 0.66  | 98 %         | Flyback                         | PV local MPPT |

| [43]              | E2E           | -               | 92 %         | Single inductor HB              | -             |

| [56]              | B2E           | -               | 95 %         | DAB                             | Data center   |

| [44]              | E2E           | From 0 to 0.66  | 95 %         | Single inductor HB              | PV local MPPT |

| [58]              | E2E           | From 0 to 0.5   | 95 %         | Single inductor HB              | PV local MPPT |

| [61]              | E2E           | From 0 to 0.15  | -            | Single inductor HB              | PV local MPPT |

| [62]              | B2E           | From 0 to 0.66  | 97 %         | Flyback                         | PV local MPPT |

| [63]              | B2E           | -               | 93.3 %       | Switched capacitor              | PV local MPPT |

| [64]              | B2E           | From 0 to 0.3   | 95 %         | LLC resonant voltage multiplier | PV local MPPT |

| [54] <sup>1</sup> | B2E           | From 0 to 0.6   | -            | Flyback                         | PV local MPPT |

Table 2.1. Key parameters extracted from the literature around DPC.

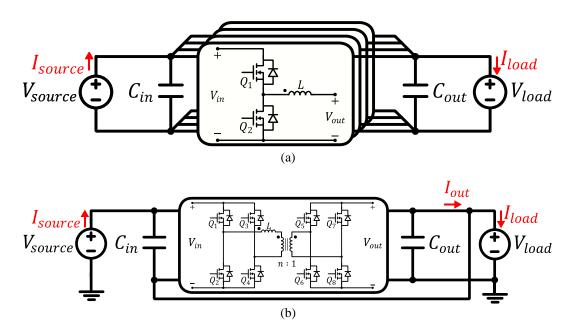

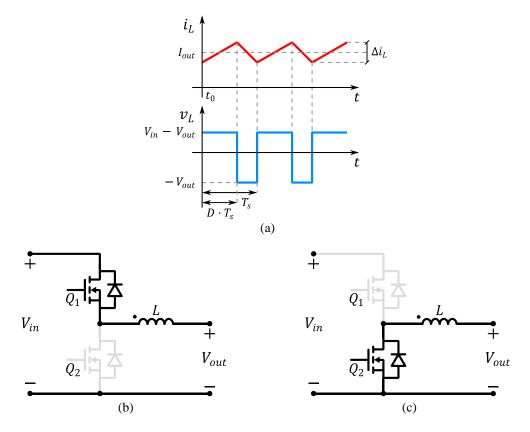

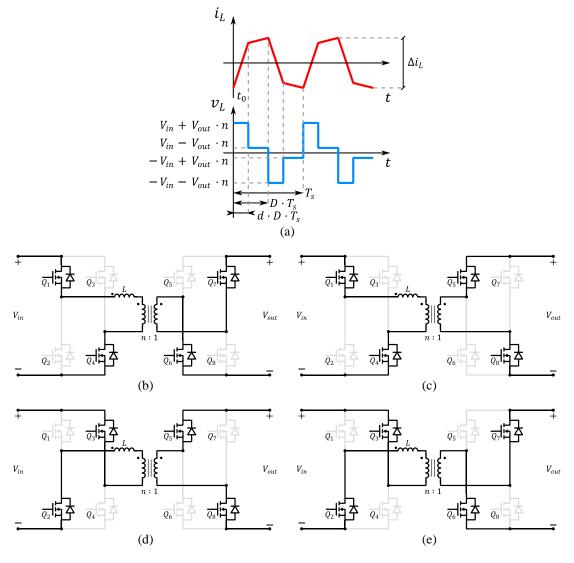

### 2.1.2 Partial Power Converters

PPCs main goal is to control the power flow between a source and a load with different voltage level. In PPC literature, there also exists a wide variety of names to refer to the same architecture, which leads to confusion.

The first time that this type of architectures were presented, they were defined as series connected boost units (SCBU) [25]. Later, novel architectures were presented and the name SCBU became obsolete. Therefore, authors from [65] introduced the terms "Input-Parallel-Output-Series" (IPOS) and "Input-Series-Output-Parallel" (ISOP), which describe the way in which the converter is connected to the source and the load. However, terms such as "partial rated charging converter" [28], [66] or "series connected PPP converter" [67] still can be found in the literature. Apart from that, the term "step-down PPC" is used in [68]–[70] to refer to different architectures. In conclusion, there exists a lack of agreement on the terms used for naming the different PPC architectures. Therefore, in order to propose a naming criteria, this document will follow the criteria

<sup>&</sup>lt;sup>1</sup> The results are not experimental. They are obtained from simulations.

proposed in [65]. This means describing the connection options between the source, the load and the power converter: Input-Series/Parallel-Output-Parallel/Series.

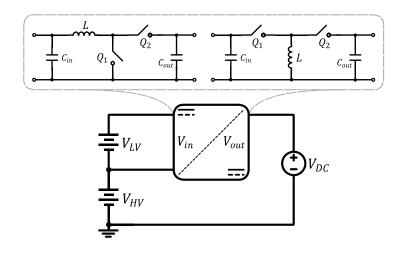

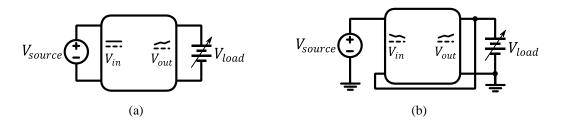

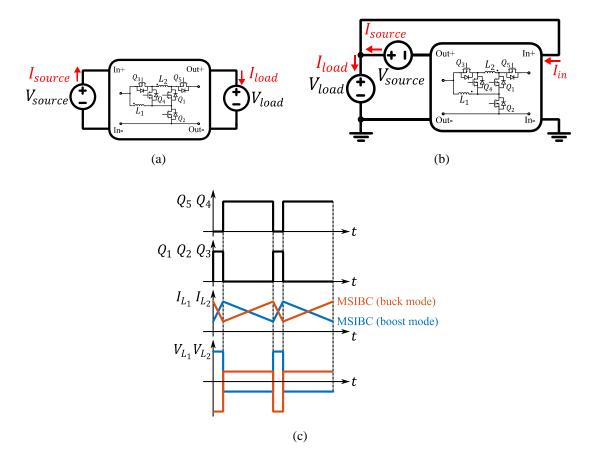

PPC architectures are divided into two main groups: PPC architectures that require galvanically isolated topologies (such as, Flyback) and PPC architectures that do not require galvanically isolated topologies.

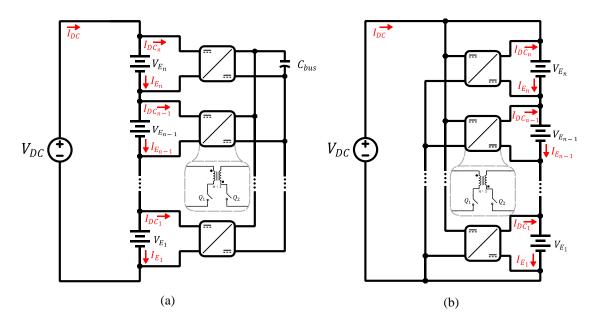

#### PPC architectures that require isolated topologies

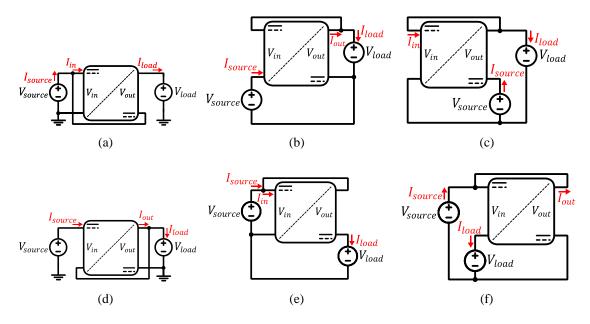

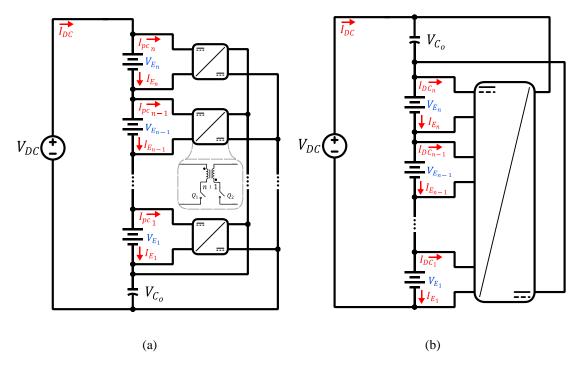

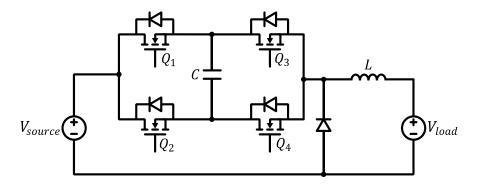

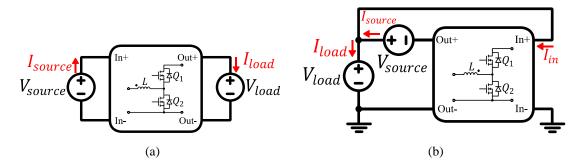

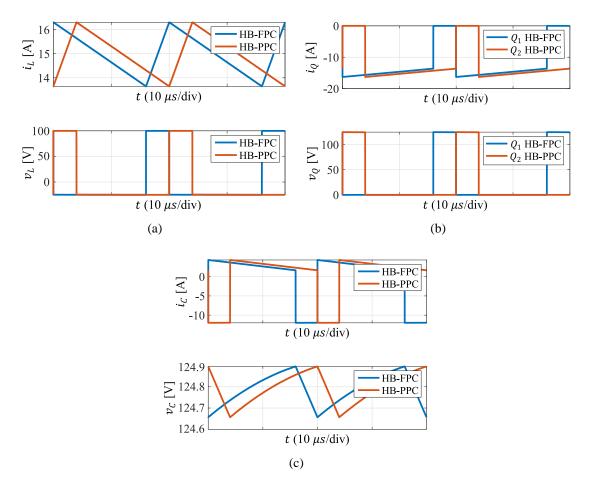

Fig. 2.4 shows the six PPC architectures found through the literature that require isolated topologies. If a non-isolated topology is implemented in any of these architectures, there exists the risk of short-circuiting  $V_{source}$  (Fig. 2.4a, Fig. 2.4b and Fig. 2.4c) or  $V_{load}$  (Fig. 2.4d, Fig. 2.4e, and Fig. 2.4f).

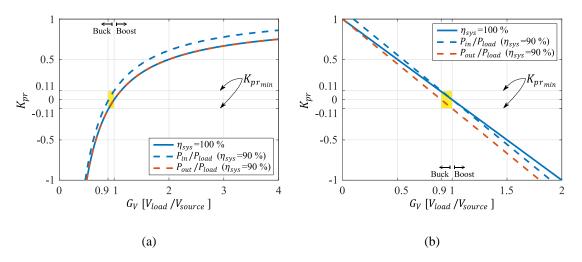

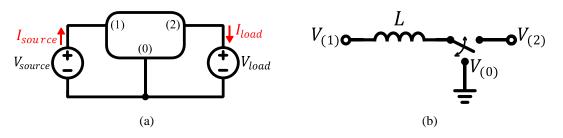

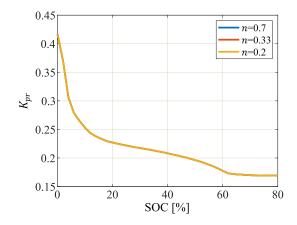

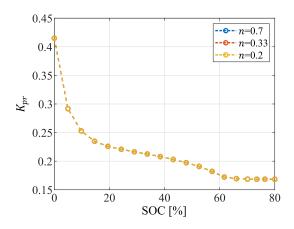

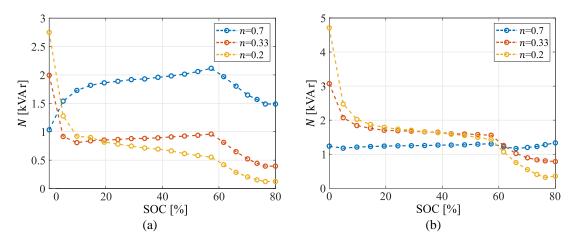

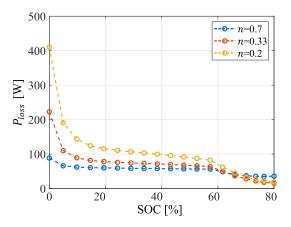

Despite the literature presents the six PPC architectures from Fig. 2.4 as different solutions, by analysing their  $K_{pr}$  it is concluded that all of them are the same. To explain this, the IPOS step-up architecture from Fig. 2.4a is taken as example. Applying Kirchhoff's laws, equations (2.5),(2.6) are obtained. Then,  $K_{pr}$  is defined as the division between the power processed by the converter ( $P_{in}$ ) and the load power ( $P_{load}$ ), see (2.7). Applying equations (2.5), (2.6) on (2.7), the  $K_{pr}$  curve of the IPOS step-up is obtained as a function of the static voltage gain ( $G_V$ ), given in (2.8),(2.9).

Fig. 2.4. PPC architectures that require isolated topologies. (a) IPOS step-up. (b) ISOP-I step-up. (c) ISOP-II step-up. (d) ISOP step-down. (e) IPOS-I step-down. (f) IPOS-II step-down.

$$V_{source} + V_{out} = V_{load} \tag{2.5}$$

$$I_{source} = I_{in} + I_{load} \tag{2.6}$$

$$K_{pr} = \frac{P_{in}}{P_{load}} = \frac{V_{source} \cdot I_{in}}{V_{load} \cdot I_{load}}$$

(2.7)

$$K_{pr_{IPOS\,step-up}} = \frac{1}{\eta_{sys}} - \frac{1}{G_V}$$

(2.8)

$$G_V = \frac{V_{load}}{V_{source}} \tag{2.9}$$

Where,  $K_{pr_{IPOS\,step-up}}$  is the processed power ratio of the IPOS step-up and  $\eta_{sys}$  is the efficiency of the system, which is given in (2.10).

$$\eta_{sys} = \frac{V_{load} \cdot I_{load}}{V_{source} \cdot I_{source}}$$

(2.10)

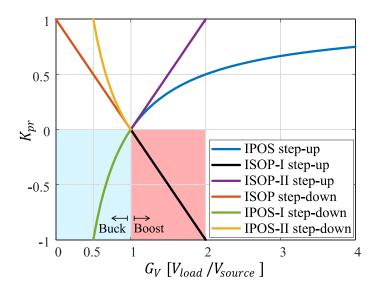

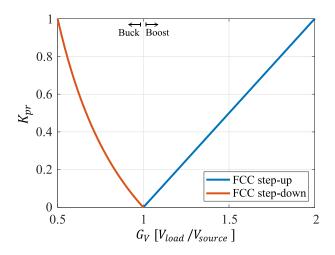

Applying the same procedure to the rest of the architectures from Fig. 2.4, the expressions shown in Table 2.2 are obtained. In order to simplify them,  $\eta_{sys}$  is substituted by  $\eta$ . The results from Table 2.2 are plotted in Fig. 2.5, where  $\eta$  is considered ideal ( $\eta$ =1).

| Architecture      | K <sub>pr</sub>                            |

|-------------------|--------------------------------------------|

| IPOS step-up      | $\frac{1}{\eta} - \frac{1}{G_V}$ $1 - G_V$ |

| ISOP-I step-up    | $\frac{1-G_V}{\eta}$                       |

| ISOP-II step-up   | $\frac{G_V}{\eta} - 1$                     |

| ISOP step-down    | $\frac{1-G_V}{\eta}$                       |

| IPOS-I step-down  | $\frac{1}{\eta} - \frac{1}{G_V}$           |

| IPOS-II step-down | $\frac{1}{G_V} - 1$                        |

Table 2.2.  $K_{pr}$  curves of the IPOS-ISOP type architectures. In order to simplify the expressions, $\eta_{sys}$  is substituted by  $\eta$ .

Fig. 2.5. Ideal K<sub>pr</sub> curves IPOS-ISOP type architectures.

From Fig. 2.5, several conclusions can be obtained:

- Voltage gain dependency: As  $G_V$  approaches 1,  $K_{pr}$  decreases for all the architectures. This means that the smaller the difference between the source and load voltage, the less power the converter will process (main objective of PPCs).

- All the architectures can be represented in one: By comparing the  $K_{pr}$  curves of the ISOP-I step-up and the ISOP-II step-up architectures, it is observed that they obtain the same absolute values. Apart from that, if the terms  $V_{in}$  and  $V_{out}$  from the ISOP-I step-up exchange their position, one can observed that the ISOP-I step-up and ISOP-II step-up architectures are the same. The only difference between them is the way in which the authors assumed their power flow as positive. The same applies to the IPOS-I step-down and IPOS-II step-down architectures.

Then, as it can be observed in Table 2.2, the  $K_{pr}$  curves of the IPOS step-up and the IPOS-I step-down architectures are the same. This is easily demonstrated by inverting the polarity of  $V_{out}$  in the IPOS step-up (Fig. 2.4a). The same applies to the ISOP step-down and the ISOP-I step-up architectures by inverting the polarity of  $V_{in}$  in the ISOP step-down (Fig. 2.4c).

Also, by comparing the IPOS step-up and the ISOP step-down architectures (Fig. 2.4a and Fig. 2.4c), it can be observed that they are the same architecture, but considering a contrary system power flow (from the source to the load and vice

versa). In conclusion, the six architectures presented by the literature (Fig. 2.4) can be considered as the same solution.

- Optimal architecture for boost applications: If the application requires only voltage boost ( $G_V$ >1), the architecture that obtains lower  $K_{pr}$  values is the IPOS step-up. In fact, its  $K_{pr}$  curve never exceeds 1 when working in boost mode. On the contrary, the ISOP-I step-up and the ISOP-II step-up obtain  $|K_{pr}|$  values greater than 1 when  $G_V$  is higher than 2. When  $K_{pr}$  is higher than 1, the converter does not operate in the partial power range, thus losing all benefits.

- Optimal architecture for buck applications: If the application requires only to reduce the voltage ( $0 < G_V < 1$ ), the architecture that obtains lower  $K_{pr}$  values is the ISOP step-down. As in the previous case, in buck mode, the ISOP step-down architecture never exceeds the value of 1 for  $K_{pr}$ . On the other hand, the IPOS-I step-down and the IPOS-II step-down architectures obtain  $|K_{pr}|$  values greater than 1 when  $G_V$  is lower than 0.5.

Based on these conclusions, from now on, the only two architectures that will be analysed from Fig. 2.4 are the IPOS step-up and the ISOP step-down. Also, in order to simplify the explanation, they will be referred just as IPOS and ISOP, respectively.

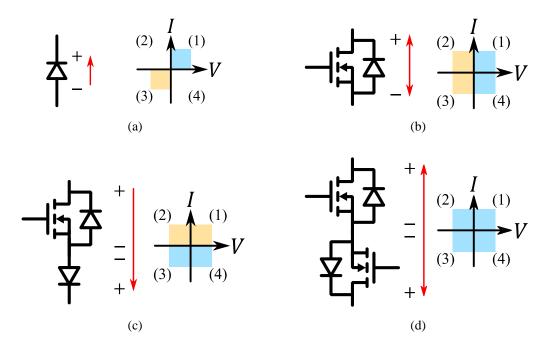

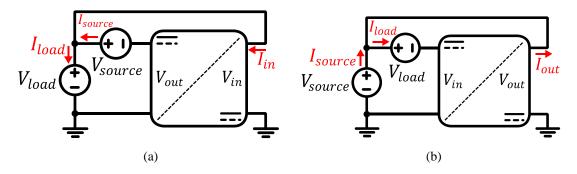

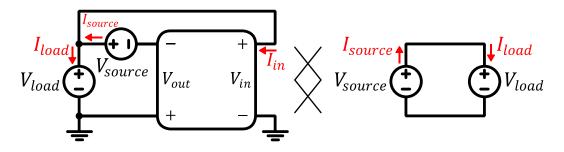

If the application requires buck-boost functionality, the selection between the IPOS and the ISOP is not so evident and it requires a more complex comparison. In other to work in voltage step-up/down applications, the power converter of a PPC architecture will enter in the shaded blue (IPOS case) and red (ISOP case) areas from Fig. 2.5. At these regions, the  $K_{pr}$  curve achieves negatives values, which means that the power flow inside the converter is reversed. This reversed power flow of the converter is demonstrated in [35], [71], [72]. In the case of the IPOS (for buck mode), the polarity of  $V_{out}$  is inverted and the flow of  $I_{in}$  changes its direction to the opposite way. Same thing occurs with the ISOP for boost mode. In this case, the polarity of  $V_{in}$  and the direction of  $I_{out}$  must be inverted. Bearing this in mind, in order to offer buck-boost functionality, the converter topology must enable bipolar voltage and bidirectional current. To explain this, a four quadrant analysis is proposed.

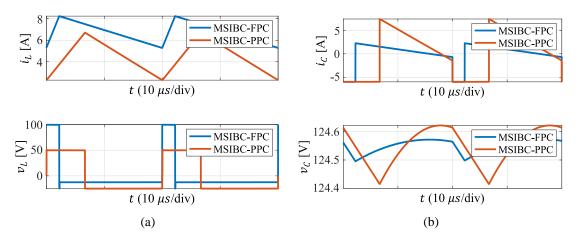

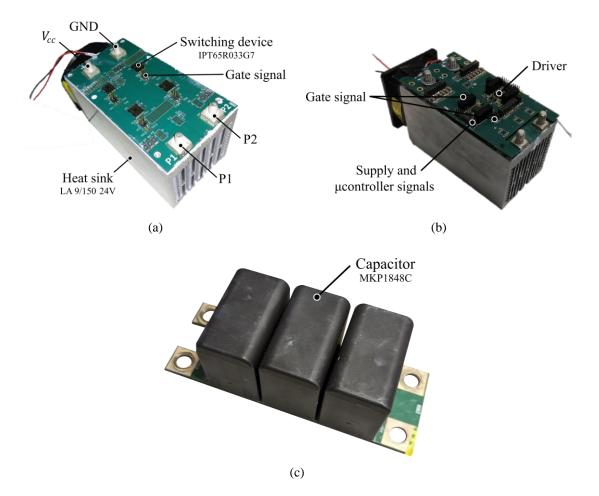

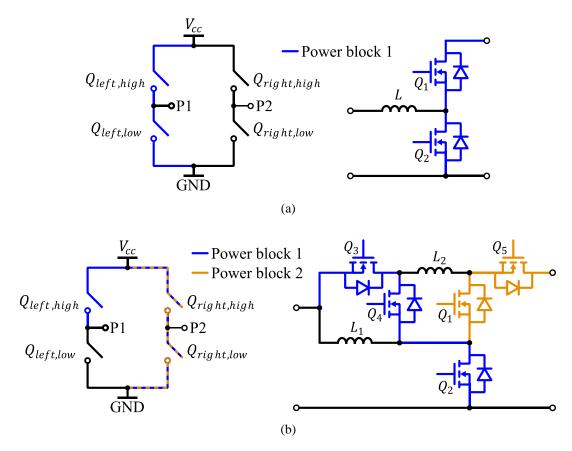

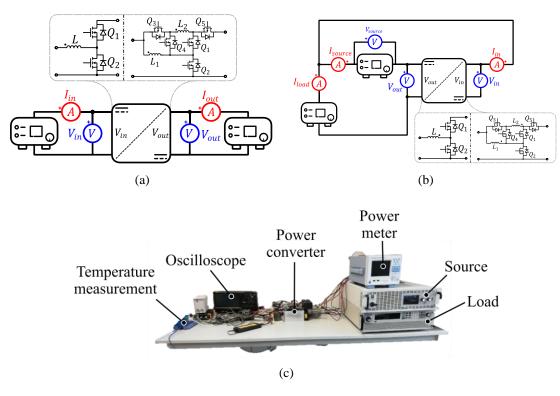

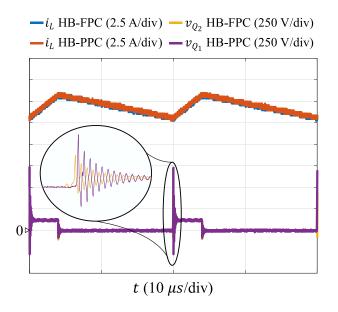

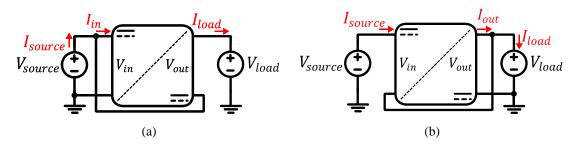

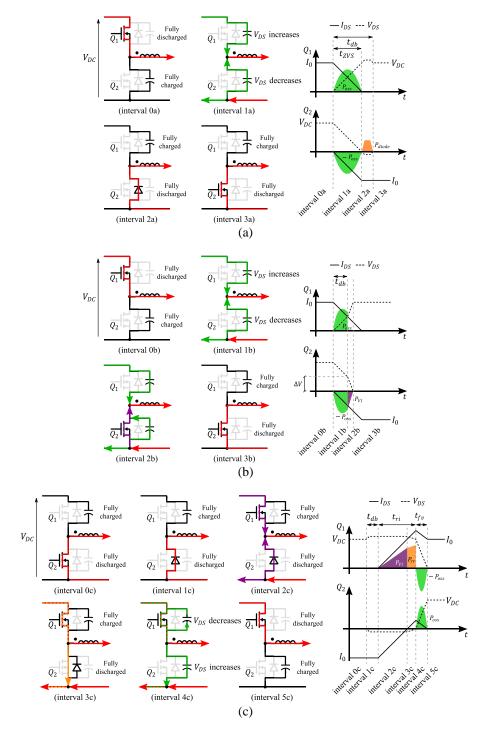

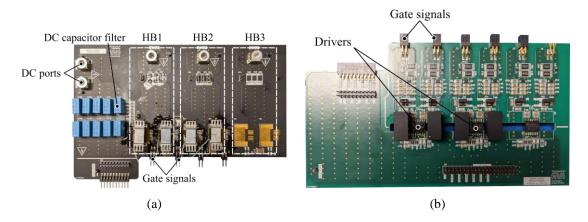

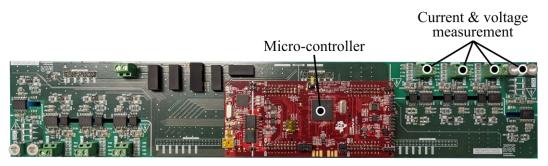

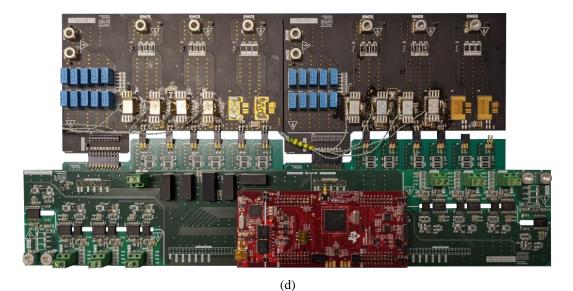

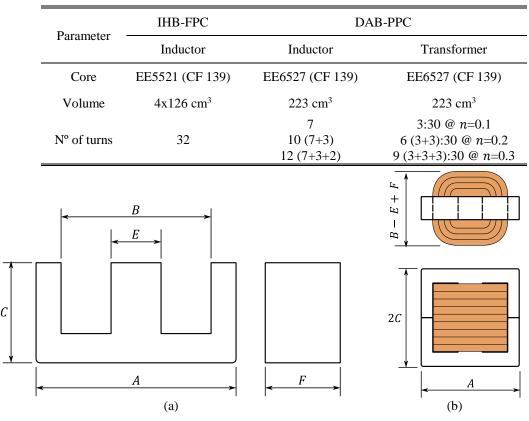

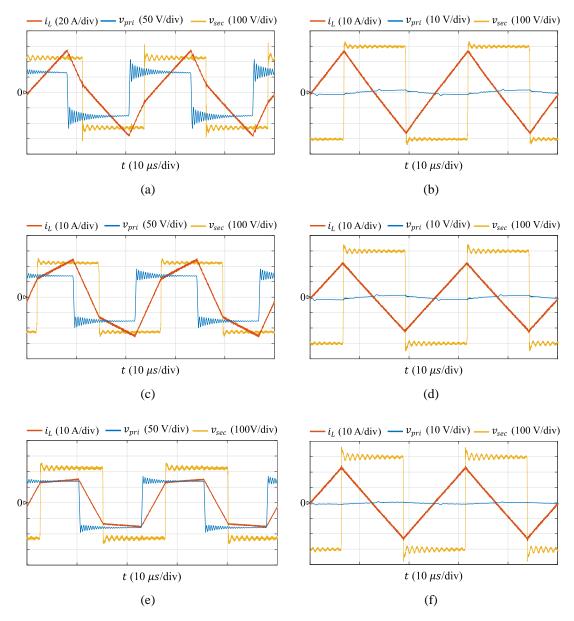

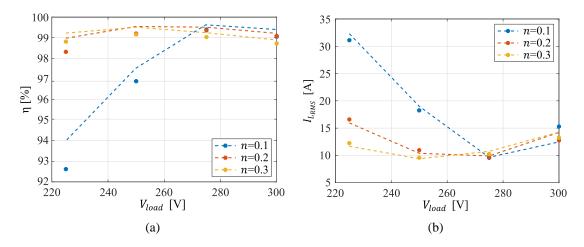

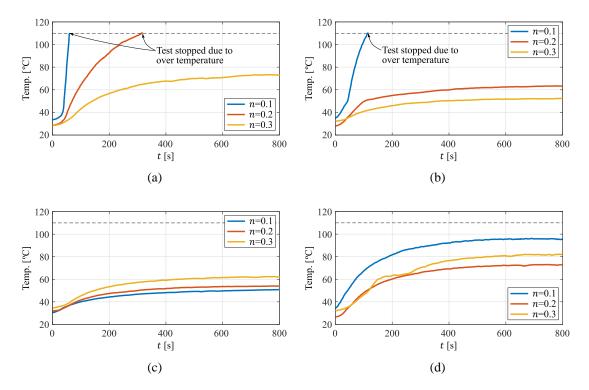

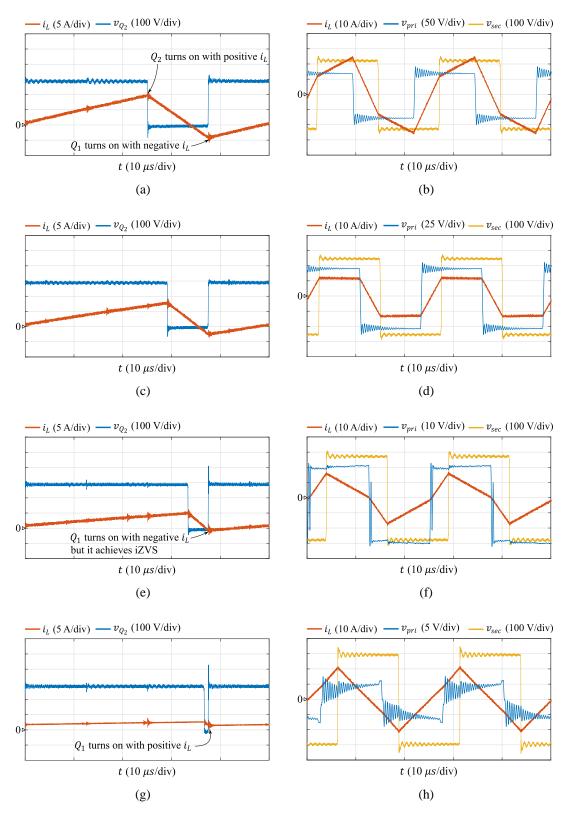

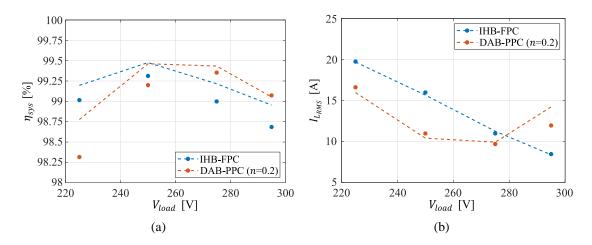

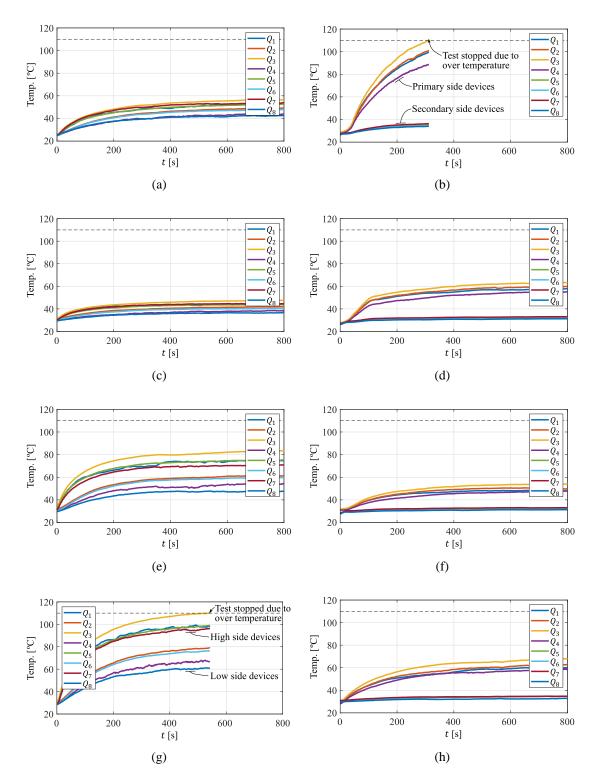

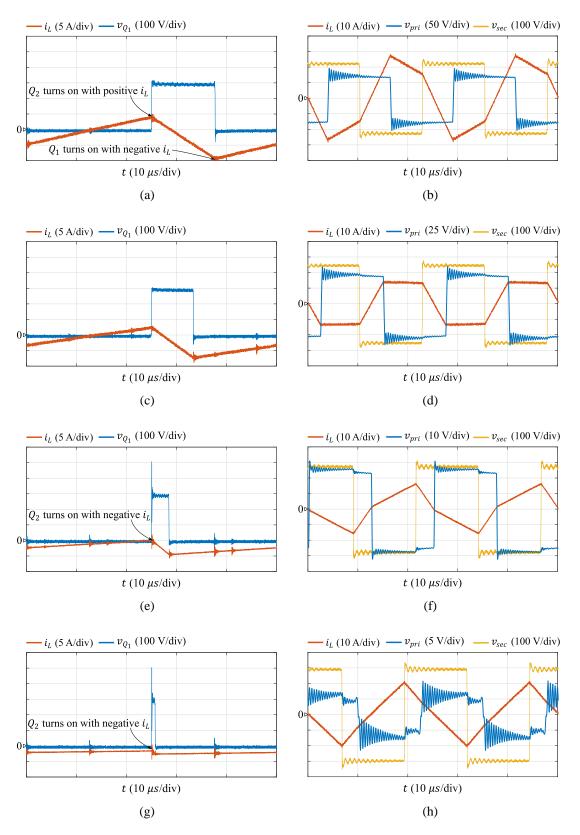

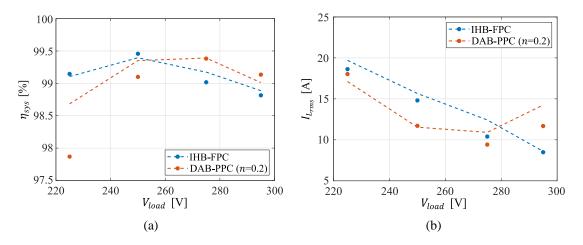

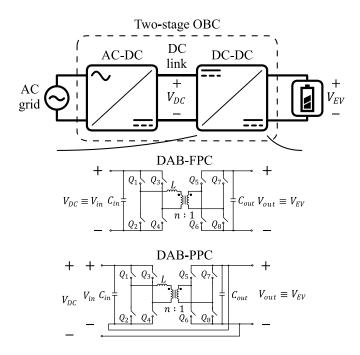

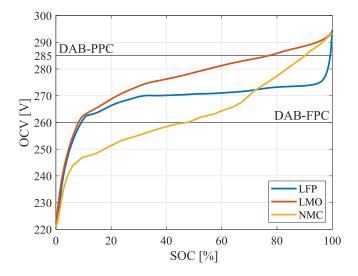

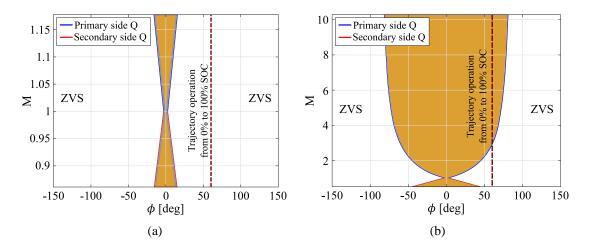

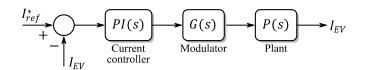

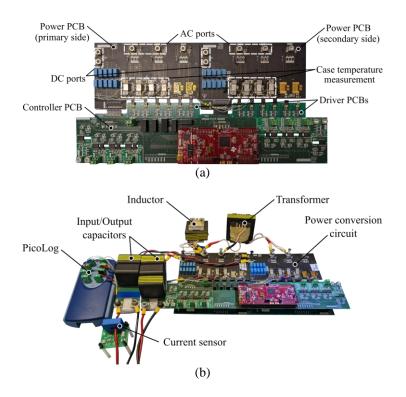

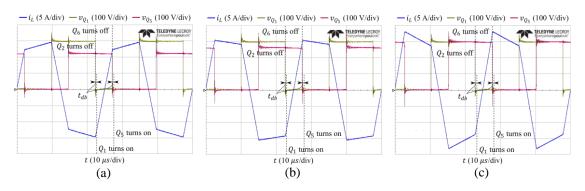

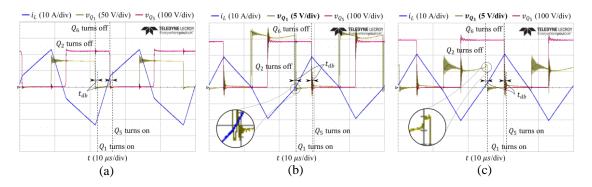

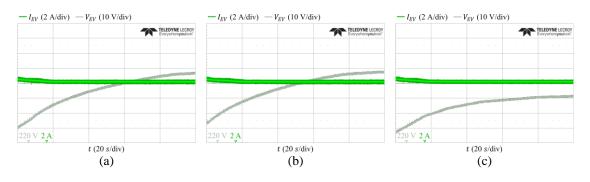

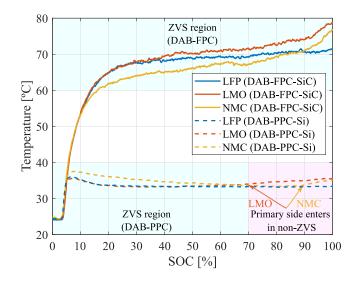

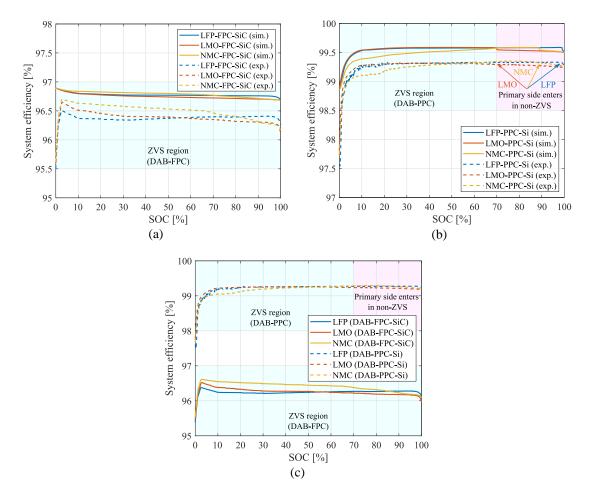

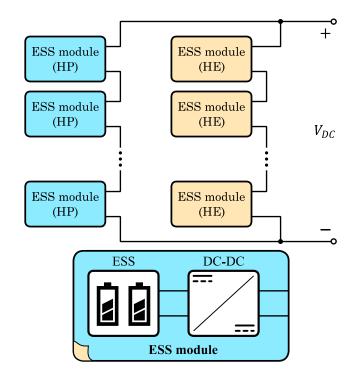

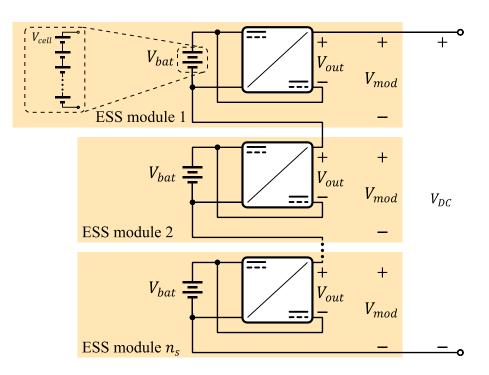

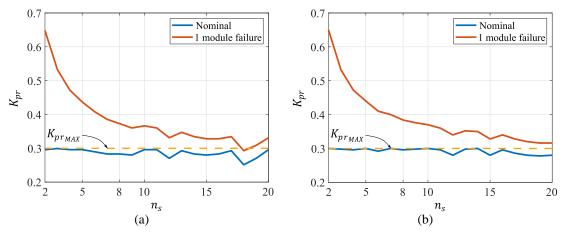

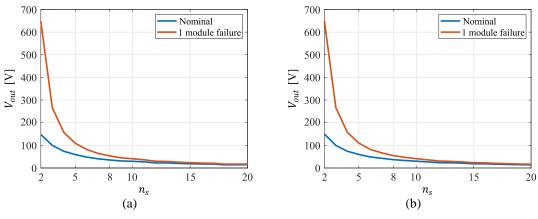

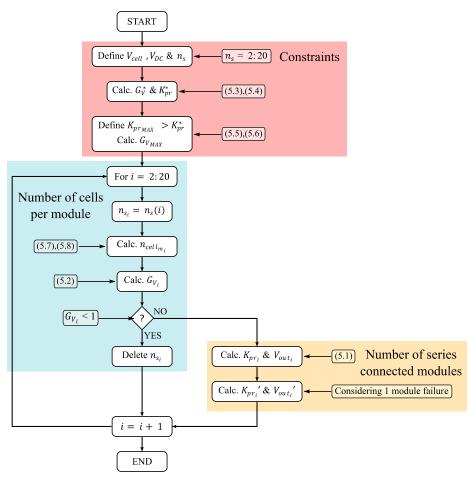

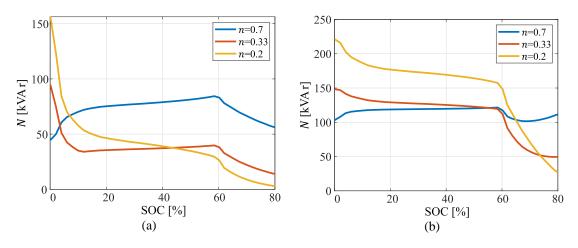

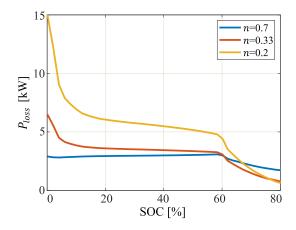

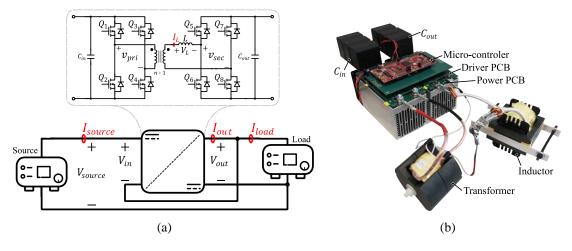

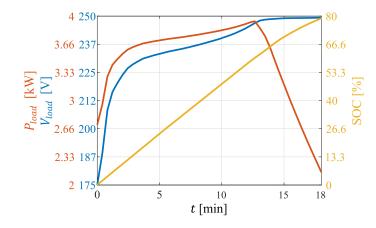

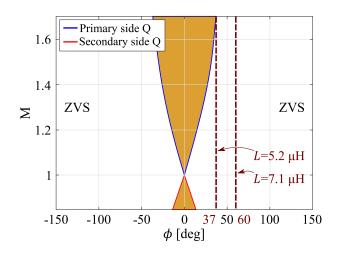

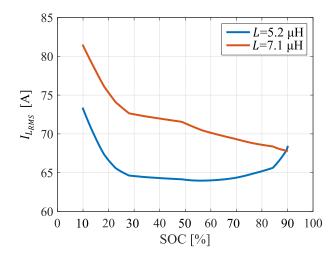

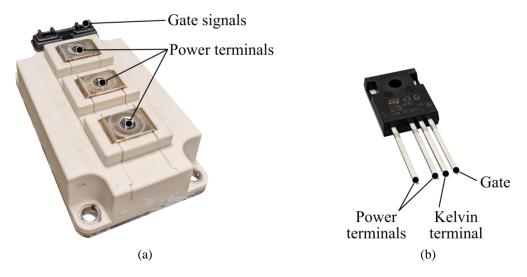

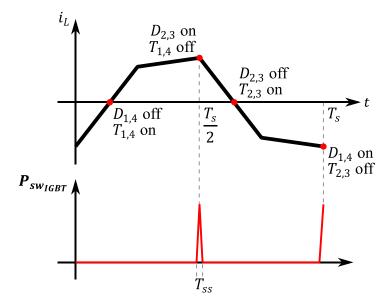

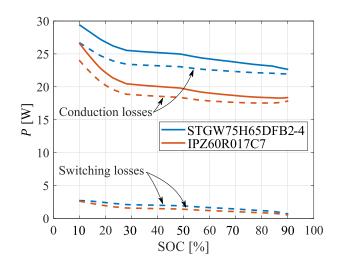

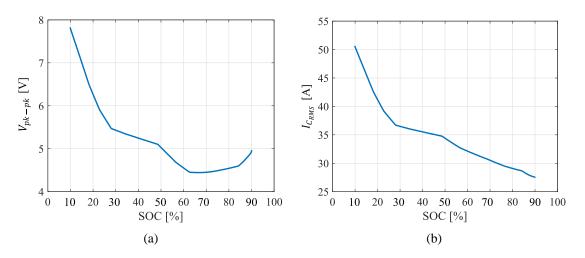

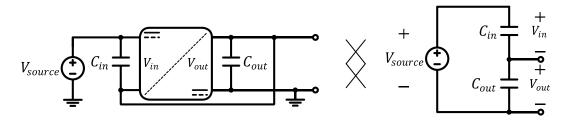

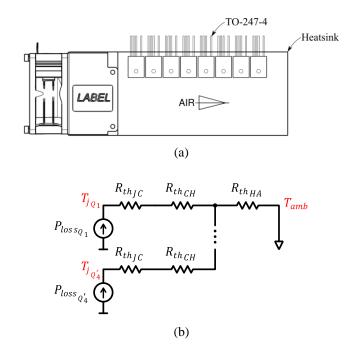

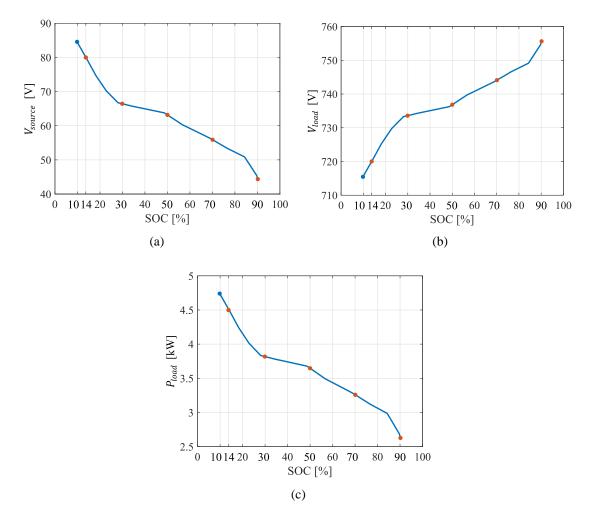

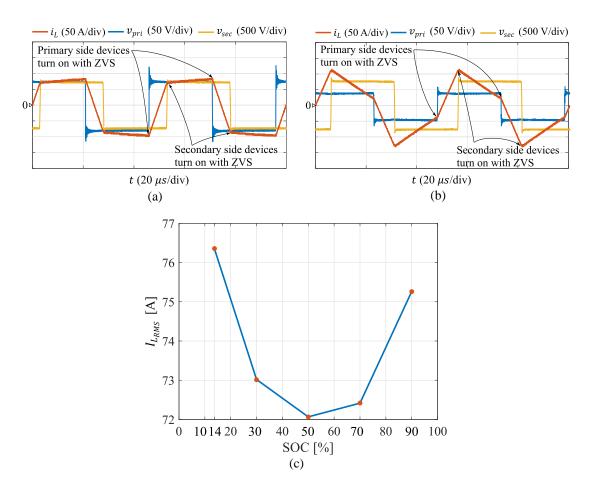

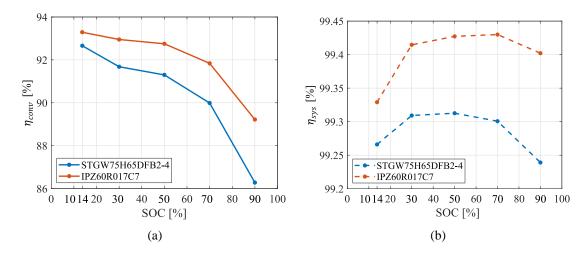

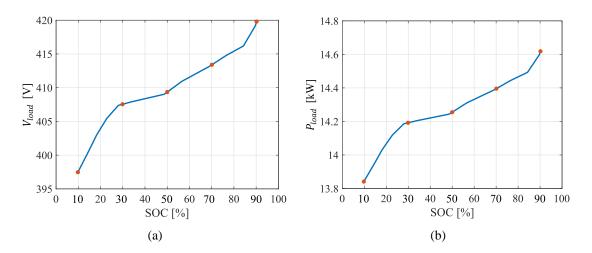

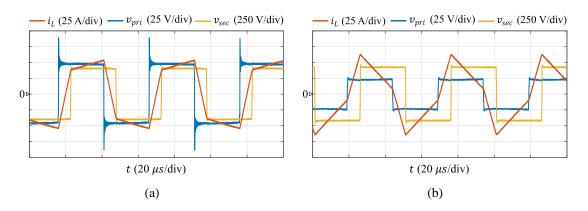

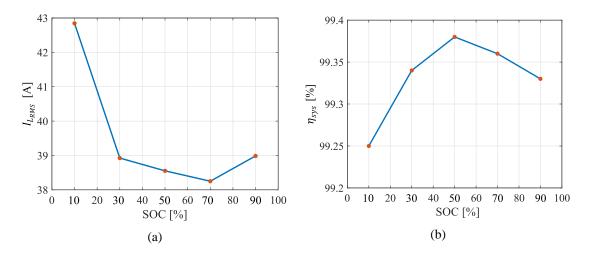

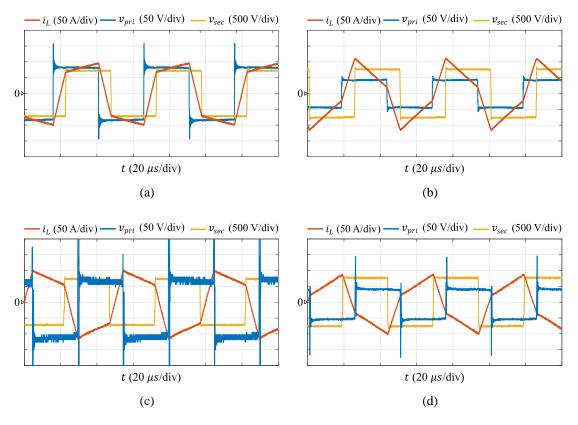

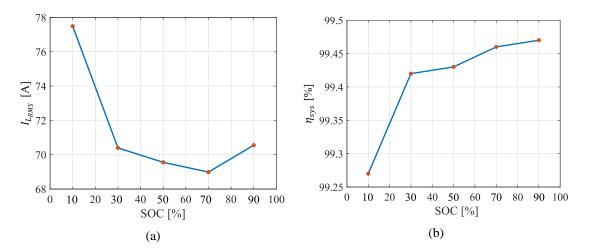

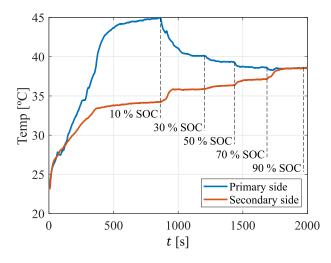

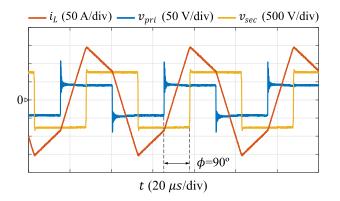

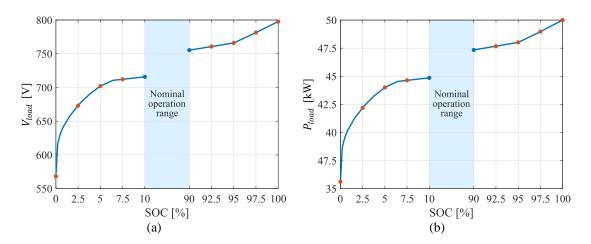

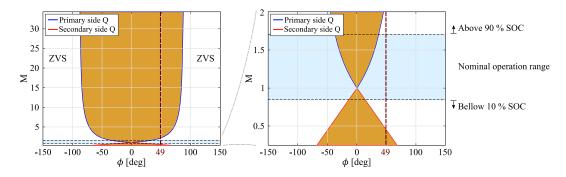

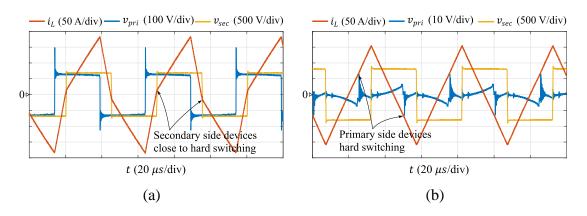

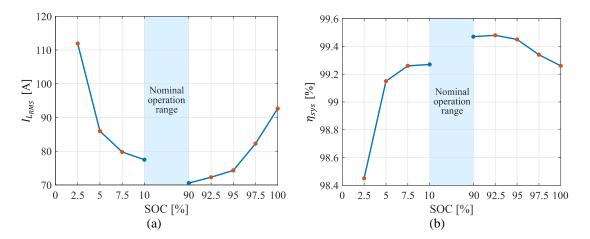

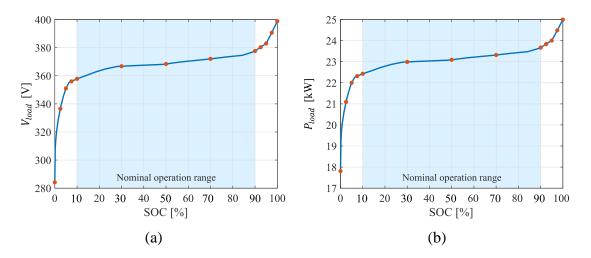

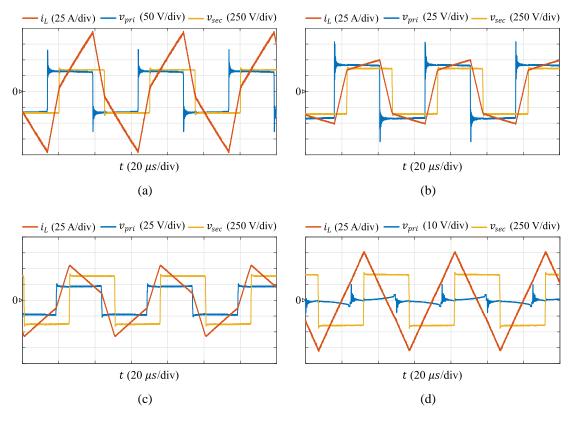

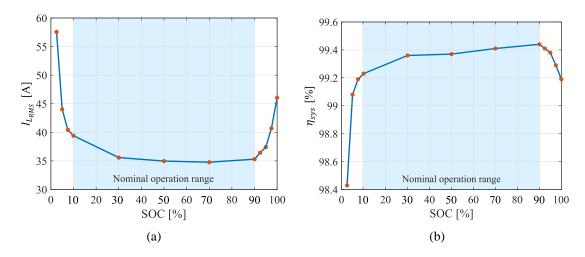

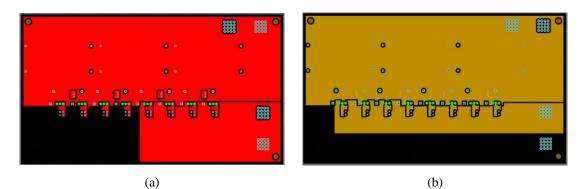

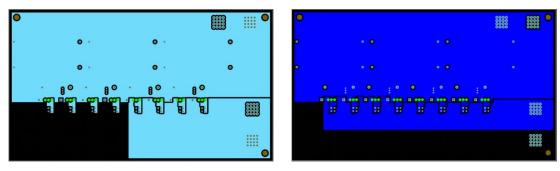

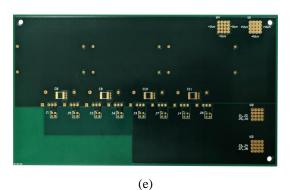

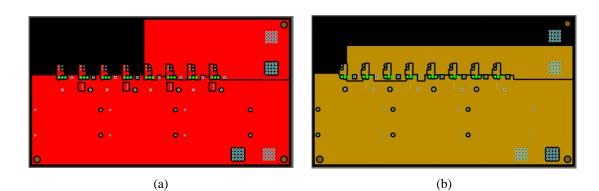

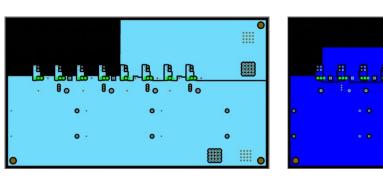

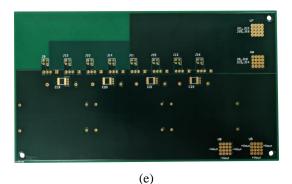

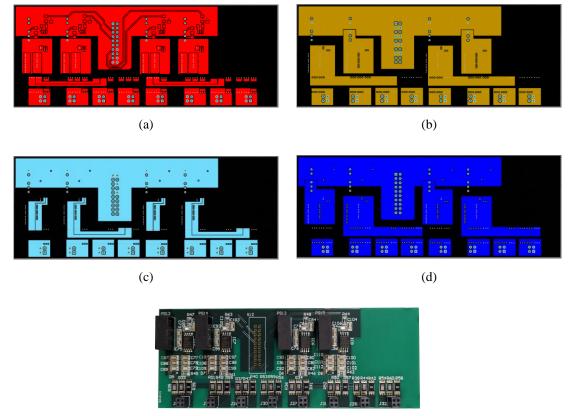

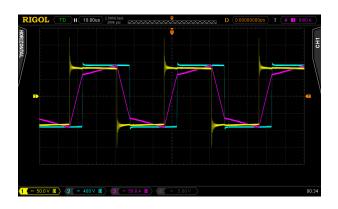

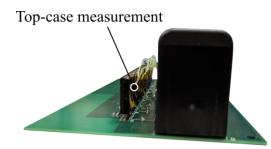

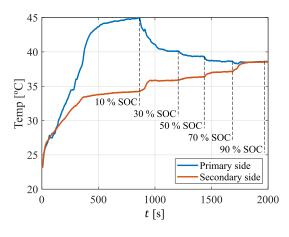

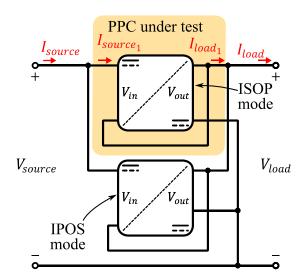

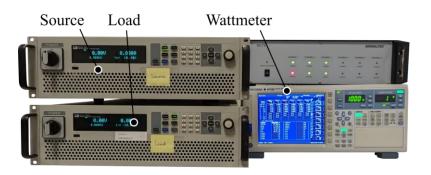

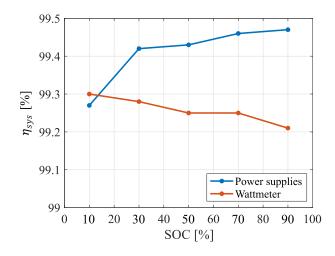

Fig. 2.6. Simplified electric diagram of an IPOS architecture.