# **DOCTORAL THESIS**

Methodology and Toolset for Testing Highly Reconfigurable Programmable Logic Controllers

MIRIAM UGARTE QUEREJETA

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No. 814078

Thesis Directors: Miren Illarramendi Rezabal Goiuria Sagardui Mendieta Iñigo Bediaga Escudero

#### Thesis directed to obtain the title of

Doctor in Applied Engineering by Mondragon Unibertsitatea

Computer and Electronics Department Faculty of Engineering Mondragon Unibertsitatea Arrasate, May 2023

"You cannot get through a single day without having an impact on the world around you. What you do makes a difference, and you have to decide what kind of difference you want to make" Jane Goodall

> Amona, Ama eta Aita. Familia eta kuadrilla

Eskerrak bihotz-bihotzez beti hor egoteagatik Miriam

### **Statement of Originality**

I, Miriam Ugarte Querejeta, declare that this thesis is the result of my personal work, and that it has not been previously submitted to obtain another degree or professional qualification. The ideas, formulations, images, illustrations taken from other sources have been duly cited and referenced.

Miriam Ugarte Querejeta Arrasate, June 2023

### Acknowledgments

This has been a long but at the same time short journey. It has not been easy doing a PhD in the middle of a pandemic, but I have finally reached the last page of my writing. This work is the result of all the people who joined me during this journey, to which I am extremely grateful.

I would like to express my deepest gratitude to my supervisors Miren Illarramendi, Leire Etxeberria, Goiuria Sagardui and Iñigo Bediaga. Leire, I am truly grateful to have had your support at the beginning and end. Your constructive feedback, guidance and positive attitude have been key in this process. Miren, despite joining the journey during a difficult time, you managed to guide me on the right path, and your encouragement gave me the boost I needed to keep going. Thank you so much for your guidance, trust, and support, which have been vital in helping me achieve this significant milestone. Eskerrik asko benetan.

I feel privileged to be part of a fantastic team – HAZI-ISI – which made me feel at home from day one. I would like to especially thank Aitor Arrieta for generously dedicating your time, effort, and commitment to helping me. I sincerely appreciate your feedback and rigorous review in improving the quality of our article. I would also like to acknowledge Pablo Valle for offering his valuable time to assist me.

Sharon, I truly appreciate your great efforts in refining my work. Thank you for your unconditional support, guidance, and patience over these three years, particularly within the last few months.

My colleagues at IDEKO. I am fortunate to have had such an outstanding mentor as Gorka. You embody the essence of commitment. Working with you has been a great experience, which brought a sense of fun and excitement into my work, keeping me up and motivated. Jon Peñalper, for assisting me with the Test Suite environment, and Jose Luis for dedicating so much time and effort to helping me. Your professionalism and commitment are truly appreciated. You all made my stay at IDEKO a joyful and fruitful experience.

Thanks to my colleagues at the University of Nottingham – Jack, Svetan, Joe H, Joe G, Joel, Giovanna, Dave S, Dave B, Fan, Agajan, Hamood, Karina, Sara, Karol, Basem... – for making the secondment a fruitful experience, and many thanks Helena, Kryssa and Nancy for organising everything. I would also like to thank my colleagues at KTH – Antonio Maffei, Fabio Monetti and Eleonora Boffa – for welcoming me warmly, the days seemed brighter than they were.

My DiManD family – Hien, Joaquin, Angela, Agajan, Fan, Hamood, Jose, Trunal, Luis, Terrin, Nathaly, Fabio – I hope to keep in touch with you. Thank you Miren and

Felix for your great commitment to managing this project.

My colleagues of Galarreta, Galarreta PhD students, and former PhD students for very warmly hosting me at your faculty.

Mondragon University and DiManD for giving me the opportunity to work on this thesis.

Eskerrik asko nere kuadrilla, Londoneko kuadrilla, my Inmarsat family, eta alboan egon zareten gainontzeko lagun guztiak, arnasgune izan baitzarete. Zuekin hau eta beste horrenbeste momentu ospatzeko desiatzen.

Azkenik, nere familia osoaren babesa eskertu nahiko nuke. Eskerrik asko bihotzbihotzez Amona, Ama, Aita, "Andoni", eta nola ez, Xenek, beti pozez irrikan agurtzeko ate ondoan egotegatik.

## Abstract

The manufacturing industry has entered a new era of highly changeable customer requirements and tailor-made products. To meet market demands, manufacturing systems need to be redefined to be able to cost-effectively produce a wide variety of products. Sustainability is key in this endeavour, maximising the utilisation of all available resources to address new bills of processes. To achieve this, however, the development of new capabilities are imperative to seamlessly adapt the manufacturing sector to the new paradigm.

At the core of the production system, the Programmable Logic Controller (PLC) orchestrates all necessary resources to initiate new processes, including modifications to the PLC program. For this reason, PLC software must be thoroughly tested after each adaptation, to ensure operational safety. At present, testing is conducted during commissioning, which typically takes place at the end of the development process, resulting in a significant impact in time and cost. In addition, the manual nature of testing practices requires considerable effort, and leaves the PLC open to errors. All these issues are further compounded in frequently changing and adaptive environments, hence the need to adopt new practices.

In this research project, therefore, we present an automated and cost-effective methodology to test highly reconfigurable PLC programs in industry. The presented approach is industry oriented, and thus we focus on the transfer of best-practices in software engineering, to the manufacturing environment. To this end, we introduce a theoretical virtual commissioning framework to enhance commissioning practices. Moreover, our approach is based on testing the logic of Functional Block Diagram (FBD) programs, one of the most widely employed PLC programming languages in Europe. Our methodology comprises the generation of the test cases based on the IEC 61131-3 standard, cost-effective test selection of the test cases, and simulation-based testing in commercially used automation solutions (the Siemens TIA portal) with the use of test oracles.

The proposal is validated with two real industrial case studies: 1) Omnifactory, which is the future automated aerospace assembly demonstrator, recently launched

at the University of Nottingham, and 2) the machine tool manufacturing industry at Danobatgroup. The results demonstrate that by automating conventional practices our methodology can effectively test real industrial PLC programs, which ultimately reduces costs and time, and ensures the reuse of available resources.

## Laburpena

Manufaktura-industria aro berri batean murgiltzen ari da, bezeroen eskari neurrigabeak eta neurrira egindako produktuen beharrak bultzatuta. Merkatuaren beharrak asetzeko asmotan, errentagarriak diren fabrikazio-sistemak berriro definitu beharrean aurkitzen gara. Jasangarritasuna kontutan hartzea funtsezkoa da prozesu honetan, eskura dauden baliabideak berrerabiliz prozesu berriak burutu ahal izateko. Halaber, era berri honi aurre egiteko digitalizazioak bultzatutako teknologia eta ezagutza berriak baliatu behar ditugu.

Kontrolatzaile logiko programagarriak (PLC-ak) industria automatizazioan erabiltzen diren gailu elektronikoak izanik, egoera berriei erantzuteko bere baitan dauden baliabide guztiak uneoro kudeatu behar dituzte. Prozesu honek aldiz, PLC-aren softwarea aldatzea dakar. Hori dela eta, sistemak behar bezala funtzionatzen duela bermatzea ezinbestekoa da, hots, aldaketen ostean akatsik egon ez dela egiaztatzea. Tradizionalki hau eskuz egin ohi den jarduera da, ahalegin haundiak eskatzen dituelarik. Honetaz gain, sistemaren funtzionamendu egokia ez da azken momentura arte begiratzen, eta ondorioz, ezusteko akatsak aurkitu izan ohi dira. Uneoroko aldaketak eskatzen dituen era berri honek, arazo guzti hauek are gehiago larrituko lituzke.

Tesi honek PLC-en software-ari zuzendutako test jarduera automatizatu eta eraginkor bat aurkeztea du helburu. Gauzak honela, Europa mailan gehien erabiltzen den PLC lengoaietako batetan oinarritzen gara, zehazki FBD lengoaian. Lehenik eta behin, biki digitaletan oinarritutako esparru teoriko bat proposatzen da, jarduera hauek modu eraginkor batetan aplikatu daitezen. Garatutako metodologiak hiru urrats nagusi ditu: 1) IEC 61131-3 estandarrean oinarritutako test instantziak sortzea, 2) test hauen optimizazioa, eraginkorrenak soilik aukeratze aldera, eta 3) test jarduerak merkatuan aurkitzen diren simulazio testuinguruetan exekutatzea, horretarako orakulu testak erabiliz.

Industriara bideratuko tesia izanik, industrian gehien erabiltzen den automatizazio soluzioetako batetan inplementatu da, hain zuzen Siemens-eko TIA Portal produktuan. Honekin batera, software ingeniaritzako jarduerak eta jakintza industriara eramatea lortu da. Metodologia balioztatzeko, industriako bi kasu erreal erabili dira: 1) Omnifactory, Nottinghameko Unibertsitatean garatutako etorkizuneko aeroespazioko muntaketara bideratutako automatizazio plataforma, eta 2) makina-erreminten fabrikazio-industrian Danobatgroup-eko makinak kudeatzen dituen PLC-a. Emaitzen arabera, aurkeztutako metodologia test jarduerak modu eraginkorrean automatizatzeko gai da, azken finean, kostuak eta denbora murriztuz, eta baliabideen berrerabiltasuna uztartuz.

## Resumen

La industria manufacturera se está embarcando en una nueva era, impulsada por una demanda sin precedentes y una necesidad de productos hechos a medida. De este modo, los sistemas de fabricación deben redefinirse para poder producir una gran variedad de productos de manera rentable. La sustentabilidad es clave en este proceso, prestando especial atención a la reutilización de los recursos disponibles para abordar nuevos procesos. Sin embargo, para adaptar la industria al nuevo paradigma exitosamente, es necesario el desarrollo de nuevas capacidades impulsados por la digitalización.

El controlador lógico programable (PLC) es la unidad central del sistema de producción, y debe de orquestar todos los recursos necesarios para abordar nuevos procesos. Esto implica modificaciones en el programa del PLC. Por lo tanto, el software del PLC requiere un proceso de verificación y validación exhaustivo para garantizar la correcta funcionalidad del sistema. Tradicionalmente, este proceso se lleva a cabo durante la puesta en marcha, donde se testea todo el sistema por primera vez. En general, los sistemas son manualmente testeados durante este proceso, el cual requiere un esfuerzo significativo y que en gran parte esta sujeto a errores. Todos estos problemas se agravan aún más en entornos donde los cambios son frecuentes, y por lo tanto existe la necesidad de adoptar nuevas prácticas.

En esta tesis se presenta una metodología automatizada para testear PLCs altamente reconfigurables de una manera eficaz y efectiva en la industria. Primeramente, se ha propuesto un marco teórico donde los gemelos digitales son clave para mejorar las prácticas de la puesta en marcha. De este modo, el trabajo principal de esta tesis se ha centrado en testear la lógica de los programas FBD, uno de los lenguajes de programación de PLC más utilizados en Europa. La metodología cosiste principalmente de tres pasos, 1) generación de los tests basados en el estándar IEC 61131-3, 2) optimización de los tests para seleccionar los más eficaces y efectivos, y 3) testeo de PLCs basado en entornos de simulación comerciales mediante el uso de oráculos.

Esta tesis está orientado a la industria y, por lo tanto, la solución expuesta se ha implementado en el entorno TIA Portal de Siemens, transfiriendo las buenas prácticas

de ingeniería de software a la industria. De este modo, la propuesta se ha validado con dos casos de estudio industriales reales 1) Omnifactory, el futuro demostrador de ensamblaje aeroespacial automatizado desarrollado en la Universidad de Nottingham, y 2) Industria de fabricación de máquina-herramienta en Danobatgroup. Según los resultados, la metodología presentada es válida para automatizar el testeo de programas PLC industriales eficazmente, lo que en definitiva reduce costes y tiempo, y permite la reutilización de los recursos.

# Contents

|    | State | ement of | Originality                    |

|----|-------|----------|--------------------------------|

| PA | RT    | I FO     | UNDATION AND CONTEXT 1         |

| 1  | Intro | oductio  | n                              |

|    | 1.1   | Motiva   | tion and Scope of the Research |

|    | 1.2   | Resear   | ch Methodology                 |

|    | 1.3   | Techni   | cal Contributions              |

|    | 1.4   | Publica  | ations                         |

|    |       | 1.4.1    | Journal Articles               |

|    |       | 1.4.2    | International Conferences      |

|    |       | 1.4.3    | Workshops                      |

|    | 1.5   | Other I  | Related Activities             |

|    |       | 1.5.1    | Dissemination                  |

|    |       | 1.5.2    | Service                        |

|    |       | 1.5.3    | Workpackages                   |

|    |       | 1.5.4    | Schools                        |

|    |       | 1.5.5    | Integrated Project             |

|    |       | 1.5.6    | Secondments                    |

|    | 1.6   | Docum    | nent Structure                 |

| 2  | Tech  | nical B  | ackground                      |

|    | 2.1   | Industr  | ry 4.0                         |

|    |       | 2.1.1    | Digital Twins                  |

|    |       | 2.1.2    | Cyber-Physical Systems         |

|    |       | 2.1.3    | Programmable Logic Controller  |

|    | 2.2   | Virtual  | Commissioning                  |

|    | 2.3   | Softwa   | re Testing                     |

|    |       | 2.3.1    | White-box Testing              |

|    |       | 2.3.2    | Mutation-based Testing         |

|    |       | 2.3.3    | Regression Testing 33          |

| 3  | State | e of the | Art                            |

|    |       |          |                                |

|   | 3.1  | Digital   | Twins in Manufacturing                                        | 36 |

|---|------|-----------|---------------------------------------------------------------|----|

|   | 3.2  | Virtual   | Commissioning                                                 | 43 |

|   |      | 3.2.1     | Digital Twin-based Virtual Commissioning                      | 43 |

|   | 3.3  | Testing   | g of FBD-based PLC Programs                                   | 44 |

|   |      | 3.3.1     | Control Flow Testing                                          | 47 |

|   |      | 3.3.2     | Data Flow Testing                                             | 48 |

|   |      | 3.3.3     | Mutation-based Testing                                        | 49 |

|   | 3.4  | Search    | -based Test Selection                                         | 50 |

|   | 3.5  | Critica   | l Analysis of the State of the Art                            | 52 |

| 4 | Indu | istrial S | urvey                                                         | 55 |

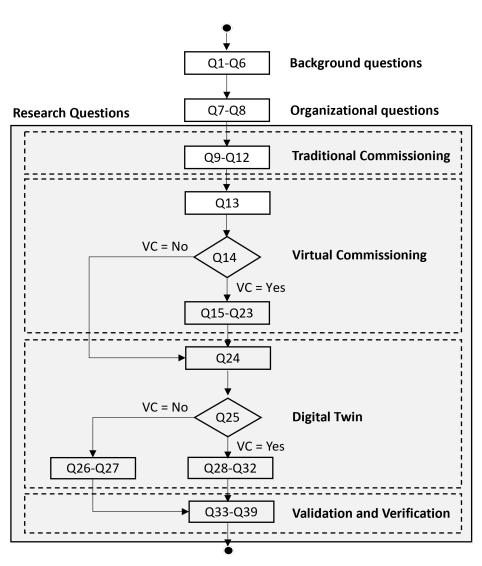

|   | 4.1  | Survey    | Design                                                        | 57 |

|   |      | 4.1.1     | Research Questions                                            | 57 |

|   |      | 4.1.2     | Target Population                                             | 59 |

|   |      | 4.1.3     | Survey Structure                                              | 60 |

|   | 4.2  | Results   | 3                                                             | 61 |

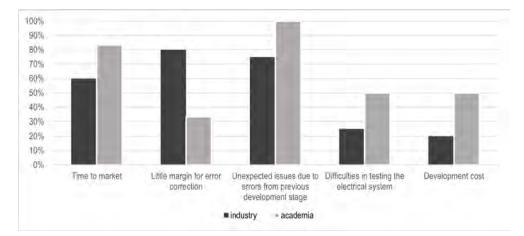

|   |      | 4.2.1     | RQ1.1. What are the main challenges in traditional commis-    |    |

|   |      |           | sioning?                                                      | 62 |

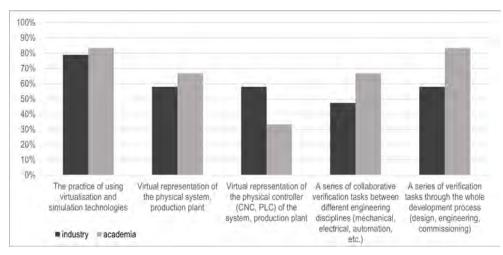

|   |      | 4.2.2     | RQ1.2. What is understood by "virtual commissioning" in       |    |

|   |      |           | industry?                                                     | 63 |

|   |      | 4.2.3     | RQ1.3. Does virtual commissioning involve different engi-     |    |

|   |      |           | neering disciplines?                                          | 64 |

|   |      | 4.2.4     | RQ1.4. Is virtual commissioning carried out at earlier stages |    |

|   |      |           | of the development process?                                   | 65 |

|   |      | 4.2.5     | RQ1.5 and RQ1.6. What are the main benefits and challenges    |    |

|   |      |           | posed by virtual commissioning?                               | 65 |

|   |      | 4.2.6     | RQ2.1. What is understood by a digital twin?                  | 66 |

|   |      | 4.2.7     | RQ2.2. What is the degree of implementation of the digital    |    |

|   |      |           | twin in industry?                                             | 66 |

|   |      | 4.2.8     | RQ2.3 and RQ2.4. What are the main benefits challenges        |    |

|   |      |           | posed by the digital twin?                                    | 67 |

|   |      | 4.2.9     | RQ3.1. What are the tests carried out during the commission-  |    |

|   |      |           | ing process?                                                  | 68 |

|   |      | 4.2.10    | RQ3.2. Are these tests automated?                             | 69 |

|   |      | 4.2.11    | RQ3.3. Is there a need for automating tests?                  | 70 |

|   |      | 4.2.12    | RQ3.4. What are the main testing challenges in the develop-   |    |

|   |      |           | ment and operation of a machine tool?                         | 71 |

|   | 4.3  | Discus    | sion                                                          | 71 |

|    | 4.4  | Threats to Validity                                      | • |   |    | 72  |

|----|------|----------------------------------------------------------|---|---|----|-----|

|    |      | 4.4.1 Internal Validity                                  | • |   |    | 72  |

|    |      | 4.4.2 External Validity                                  | • |   |    | 73  |

|    | 4.5  | Conclusions                                              | • |   |    | 73  |

| 5  | The  | oretical Framework                                       |   | • | •• | 75  |

|    | 5.1  | Research Objectives                                      |   |   |    | 76  |

|    | 5.2  | Research Hypotheses                                      |   |   |    | 77  |

|    | 5.3  | Overview of the Theoretical Framework                    |   |   |    | 78  |

|    | 5.4  | Case Studies                                             |   |   |    | 83  |

|    |      | 5.4.1 Omnifactory                                        |   |   |    | 83  |

|    |      | 5.4.2 Danobatgroup                                       |   | • |    | 85  |

|    |      | 5.4.3 KAIST Use Cases                                    |   |   |    | 86  |

|    | 5.5  | Case Studies Employed for Validating each Contribution . |   |   |    | 88  |

| PA | ART  | II TEST GENERATION                                       |   |   |    | 89  |

| 6  | FBL  | Test Generation                                          | • | • | •• | 91  |

|    | 6.1  | Introduction                                             |   |   |    | 92  |

|    | 6.2  | Overview of the Approach                                 |   |   |    | 93  |

|    | 6.3  | Test Case Generation Process                             |   |   |    | 94  |

|    |      | 6.3.1 SMT Solver                                         |   |   |    | 95  |

|    |      | 6.3.2 Generating the Yices 2 SMT2 File                   |   |   |    | 96  |

|    |      | 6.3.3 Yices 2 SMT2 Integration                           |   |   |    | 102 |

|    |      | 6.3.4 Test Case and Mutant Generation                    |   |   |    | 105 |

|    | 6.4  | Cost-effectiveness Measures and Oracles Calculation      |   |   |    | 109 |

|    |      | 6.4.1 Coverage Calculation                               |   |   |    | 109 |

|    |      | 6.4.2 Execution Time Calculation                         |   |   |    | 111 |

|    |      | 6.4.3 Fault Detection Capability Calculation             |   |   |    | 112 |

|    | 6.5  | Evaluation                                               |   |   |    | 113 |

|    |      | 6.5.1 Case Studies                                       |   |   |    | 113 |

|    |      | 6.5.2 Results                                            |   |   |    | 116 |

|    | 6.6  | Conclusion                                               |   |   |    | 119 |

| PA | ART  | III TEST OPTIMISATION                                    |   |   |    | 123 |

| 7  | Cost | -effective Test Selection for FBD Programs               |   | • | •• | 125 |

|    | 7.1  | Introduction                                             |   |   |    | 126 |

|    | 7.2  | Overview                                                 |   |   |    | 127 |

|    | 7.3  | Search-based Multi-Objective Test Selection              |   |   |    | 127 |

|    |      | 7.3.1 Cost-effective Metrics                             |   |   |    | 128 |

|    |      | 7.3.2 Fitness Functions                                  |   |   |    | 131 |

|    |      |                                                          |   |   |    |     |

|    | 7.4                                                       | Evalua                                                                                                                                  | ution                                                     | 131                                                                                            |

|----|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------|

|    |                                                           | 7.4.1                                                                                                                                   | Research Questions                                        | 131                                                                                            |

|    |                                                           | 7.4.2                                                                                                                                   | Case Studies                                              | 132                                                                                            |

|    |                                                           | 7.4.3                                                                                                                                   | Evaluation Metrics                                        | 132                                                                                            |

|    |                                                           | 7.4.4                                                                                                                                   | Algorithm Setup                                           | 134                                                                                            |

|    |                                                           | 7.4.5                                                                                                                                   | Experimental Setup                                        | 134                                                                                            |

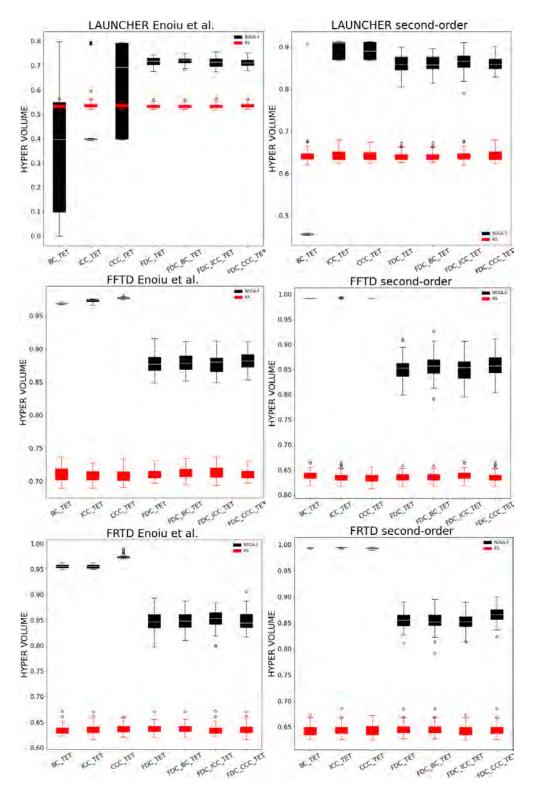

|    | 7.5                                                       | Result                                                                                                                                  | s and Discussion                                          | 135                                                                                            |

|    |                                                           | 7.5.1                                                                                                                                   | RQ8. How does the multi-objective search-based algorithm  |                                                                                                |

|    |                                                           |                                                                                                                                         | perform as compared to RS?                                | 135                                                                                            |

|    |                                                           | 7.5.2                                                                                                                                   | RQ9. Which of the defined cost-effectiveness metrics per- |                                                                                                |

|    |                                                           |                                                                                                                                         | forms best?                                               | 138                                                                                            |

|    |                                                           | 7.5.3                                                                                                                                   | RQ10. To what extent can our approach reduce TET and what |                                                                                                |

|    |                                                           |                                                                                                                                         | impact does it have on the fault detection rate?          | 140                                                                                            |

|    | 7.6                                                       | Threat                                                                                                                                  | s to Validity                                             | 143                                                                                            |

|    |                                                           | 7.6.1                                                                                                                                   | Internal Validity                                         | 143                                                                                            |

|    |                                                           | 7.6.2                                                                                                                                   | External Validity                                         | 144                                                                                            |

|    |                                                           | 7.6.3                                                                                                                                   | Conclusion Validity                                       | 144                                                                                            |

|    | 7.7                                                       | Conclu                                                                                                                                  | usion                                                     | 144                                                                                            |

| PA | RT                                                        | IV TIA                                                                                                                                  | A PORTAL TESTING                                          | 147                                                                                            |

|    |                                                           |                                                                                                                                         |                                                           |                                                                                                |

| 8  | Sim                                                       | ulation-                                                                                                                                | based PLC Testing of Siemens PLC Programs                 | 149                                                                                            |

| 8  | <b>Sim</b><br>8.1                                         |                                                                                                                                         | based PLC Testing of Siemens PLC Programs                 | <b>149</b><br>150                                                                              |

| 8  |                                                           | Introd                                                                                                                                  |                                                           |                                                                                                |

| 8  | 8.1                                                       | Introd                                                                                                                                  | uction                                                    | 150                                                                                            |

| 8  | 8.1                                                       | Introdu<br>PLC T                                                                                                                        | uction                                                    | 150<br>151                                                                                     |

| 8  | 8.1                                                       | Introdu<br>PLC T<br>8.2.1                                                                                                               | uction                                                    | 150<br>151<br>152                                                                              |

| 8  | 8.1                                                       | Introde<br>PLC T<br>8.2.1<br>8.2.2                                                                                                      | uction                                                    | 150<br>151<br>152<br>153                                                                       |

| 8  | 8.1                                                       | Introdu<br>PLC T<br>8.2.1<br>8.2.2<br>8.2.3                                                                                             | uction                                                    | 150<br>151<br>152<br>153<br>155                                                                |

| 8  | 8.1                                                       | Introdu<br>PLC T<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5                                                                           | uction                                                    | 150<br>151<br>152<br>153<br>155<br>156                                                         |

| 8  | 8.1<br>8.2                                                | Introdu<br>PLC T<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5                                                                           | uction                                                    | 150<br>151<br>152<br>153<br>155<br>156<br>158                                                  |

| 8  | 8.1<br>8.2                                                | Introdu<br>PLC T<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>Evalua                                                                 | uction                                                    | 150<br>151<br>152<br>153<br>155<br>156<br>158<br>161                                           |

| 8  | 8.1<br>8.2                                                | Introdu<br>PLC T<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>Evalua<br>8.3.1                                                        | uction                                                    | 150<br>151<br>152<br>153<br>155<br>156<br>158<br>161<br>161                                    |

| 8  | 8.1<br>8.2                                                | Introdu<br>PLC T<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>Evalua<br>8.3.1<br>8.3.2                                               | uction                                                    | 150<br>151<br>152<br>153<br>155<br>156<br>158<br>161<br>161<br>165                             |

| 8  | 8.1<br>8.2                                                | Introdu<br>PLC T<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>Evalua<br>8.3.1<br>8.3.2<br>8.3.3                                      | uction                                                    | 150<br>151<br>152<br>153<br>155<br>156<br>158<br>161<br>161<br>165<br>168                      |

| 8  | 8.1<br>8.2                                                | Introdu<br>PLC T<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>Evalua<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4                             | uction                                                    | 150<br>151<br>152<br>153<br>155<br>156<br>158<br>161<br>161<br>165<br>168<br>169               |

| 8  | 8.1<br>8.2                                                | Introdu<br>PLC T<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>Evalua<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4<br>8.3.5                    | uction                                                    | 150<br>151<br>152<br>153<br>155<br>156<br>158<br>161<br>161<br>165<br>168<br>169<br>169        |

|    | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li></ul> | Introdu<br>PLC T<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>Evalua<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4<br>8.3.5<br>8.3.6<br>Conclu | uction                                                    | 150<br>151<br>152<br>153<br>155<br>156<br>158<br>161<br>161<br>165<br>168<br>169<br>169<br>169 |

| 9.1               | Summ                                                             | ary of the Contributions                                      | 174               |

|-------------------|------------------------------------------------------------------|---------------------------------------------------------------|-------------------|

|                   | 9.1.1                                                            | Hypotheses Validation                                         | 175               |

|                   | 9.1.2                                                            | Limitations of the Proposed Solutions and the Specific Imple- |                   |

|                   |                                                                  | mentation                                                     | 178               |

| 9.2               | Perspe                                                           | ctives and Future Work                                        | 180               |

|                   | 9.2.1                                                            | Industry Transfer                                             | 180               |

|                   | 9.2.2                                                            | Application of the Proposed Methods in other PLCs             | 180               |

|                   | 9.2.3                                                            | Adoption of Sustainable Business Models towards Innovation    | 181               |

|                   | 9.2.4                                                            | Further Research                                              | 181               |

| Bibliogr          | aphy .                                                           |                                                               | 183               |

| Append            | ices                                                             |                                                               | 211               |

| Append            | ix A S                                                           | Survey Questionnaire                                          | 212               |

| Append            | ix B H                                                           | Ethics Requirements                                           | 235               |

| Append            |                                                                  | Code                                                          | 241               |

|                   | IX C C                                                           |                                                               | 241               |

| C.1               |                                                                  | tSuiteConverter.java                                          | 241<br>241        |

|                   | TIAtes                                                           |                                                               |                   |

| C.1               | TIAtes<br>genera                                                 | tSuiteConverter.java                                          |                   |

| C.1               | TIAtes<br>generat<br>Goal)                                       | tSuiteConverter.java                                          | 241               |

| C.1<br>C.2        | TIAtes<br>generat<br>Goal)<br>generat                            | tSuiteConverter.java                                          | 241               |

| C.1<br>C.2<br>C.3 | TIAtes<br>generat<br>Goal)<br>generat<br>float co                | tSuiteConverter.java                                          | 241<br>246        |

| C.1<br>C.2<br>C.3 | TIAtes<br>genera<br>Goal)<br>genera<br>float co<br><b>ix D H</b> | tSuiteConverter.java                                          | 241<br>246<br>247 |

# List of Figures

| 1.1  | General overview of the research methodology [VK15]                                  | 7  |

|------|--------------------------------------------------------------------------------------|----|

| 2.1  | Industry evolution, from Industry 1.0 to Industry 4.0                                | 19 |

| 2.2  | Five-dimensional digital twin                                                        | 21 |

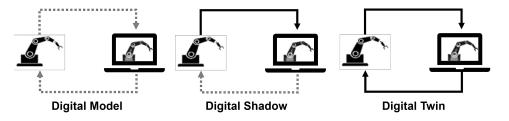

| 2.3  | Digital twin, Digital Shadow, and Digital Model – adapted from [KKT <sup>+</sup> 18] | 22 |

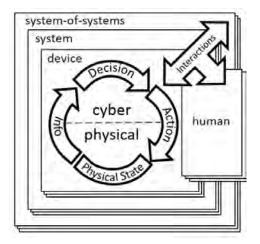

| 2.4  | CPS conceptual model [GGWB17]                                                        | 23 |

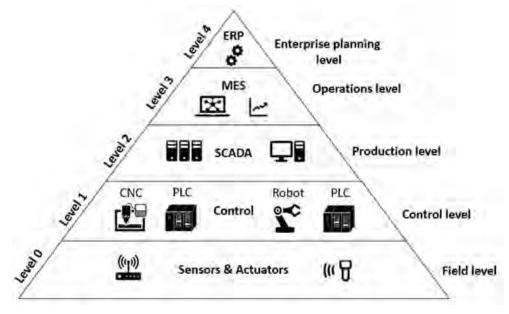

| 2.5  | Vertical integration based on the ISA-95 pyramid – adapted from [PDK19]              | 23 |

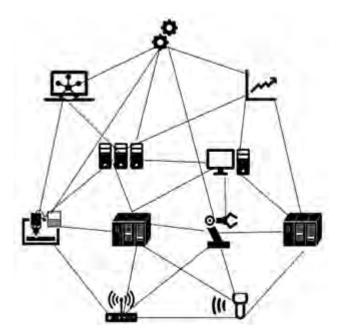

| 2.6  | Distributed and decentralised CPS architecture                                       | 24 |

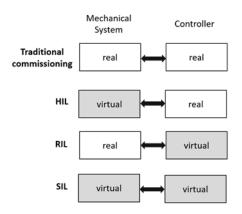

| 2.7  | CPS commissioning techniques                                                         | 27 |

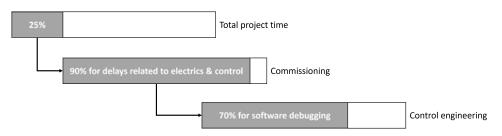

| 2.8  | Contribution of control software to project delay – adapted from [RW07]              | 28 |

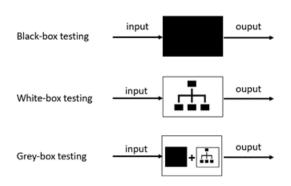

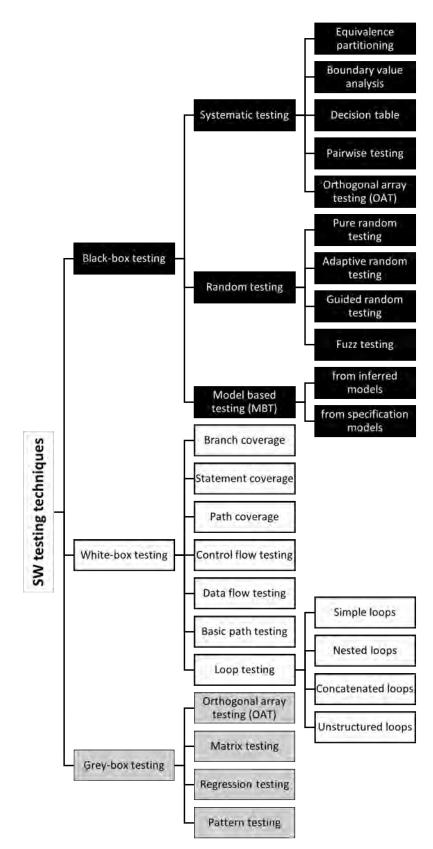

| 2.9  | Software testing methods                                                             | 30 |

| 2.10 | CPS testing methods                                                                  | 32 |

| 2.11 | Regression testing methods – adapted from [Do16]                                     | 33 |

| 3.1  | Digital twin and manufacturing related publications                                  | 36 |

| 3.2  | Classification of digital twin applications throughout the lifecycle                 | 41 |

| 3.3  | Classification of digital twin applications into development and operations          | 42 |

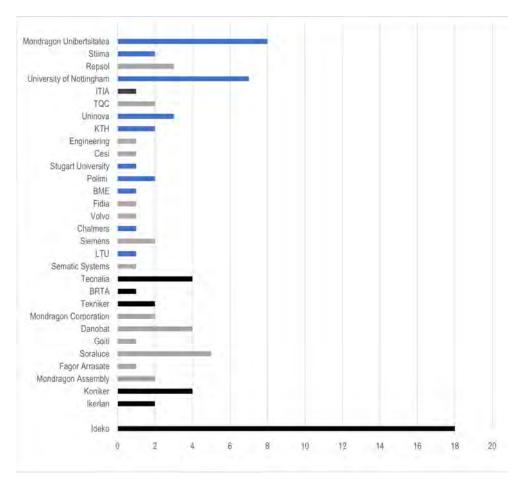

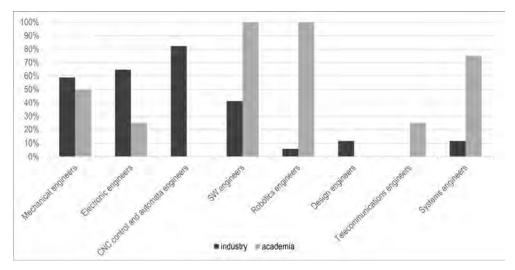

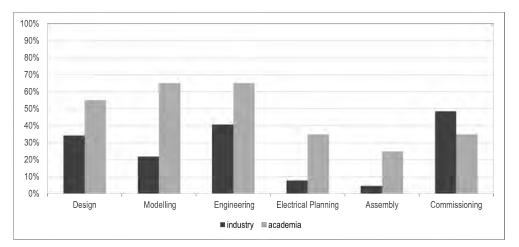

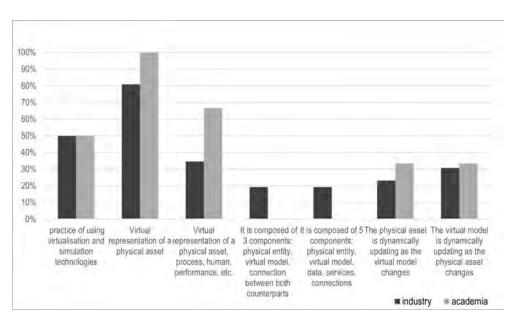

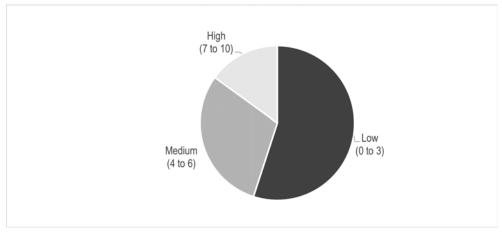

| 4.1  | Survey target population                                                             | 59 |

| 4.2  | Survey structure                                                                     | 61 |

| 4.3  | Challenges in traditional commissioning                                              | 62 |

| 4.4  | Virtual commissioning definition                                                     | 63 |

| 4.5  | Virtual commissioning practitioners                                                  | 64 |

| 4.6  | Virtual commissioning through the development process                                | 65 |

| 4.7  | Digital twin definition                                                              | 67 |

| 4.8  | Degree of implementation of the digital twin in industry                             | 67 |

| 4.9  | Validation and verification tests                                                    | 68 |

| 4.10 | Testing procedures                                                                   | 69 |

|      | Need for automating testing practices                                                | 70 |

| 4.12 | Testing challenges                                                                   | 71 |

|      |                                                                                      |    |

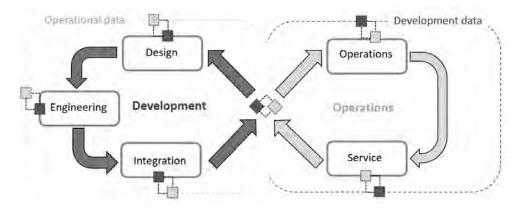

| 5.1  | Digital twin-enabled DevOps approach [QES20]                              | 78  |

|------|---------------------------------------------------------------------------|-----|

| 5.2  | Digital twin-based continuous testing of PLCs                             | 79  |

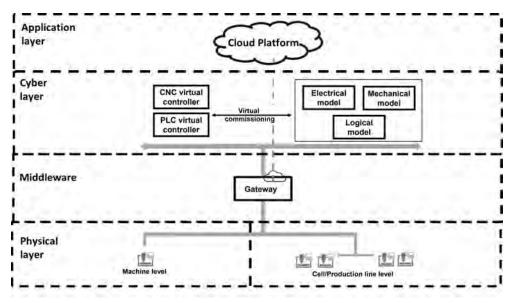

| 5.3  | Digital twin-based virtual commissioning architecture – based on [TLHN20] | 80  |

| 5.4  | Overview of the methodology                                               | 81  |

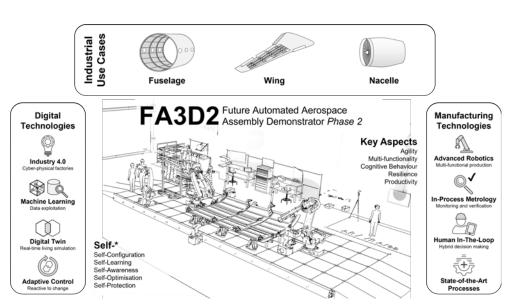

| 5.5  | Omnifactory overview [STS <sup>+</sup> 20]                                | 84  |

| 5.6  | Omnifactory system reconfiguration framework                              | 85  |

| 5.7  | PLC development process at Danobatgroup                                   | 85  |

| 5.8  | simTRIP FBD module                                                        | 87  |

| 5.9  | LAUNCHER FBD module                                                       | 87  |

| 5.10 | simGRAVEL FBD module                                                      | 88  |

| 6.1  | Test data generation overall approach                                     | 93  |

| 6.2  | Test case generation process                                              | 95  |

| 6.3  | Test case and mutant generation                                           | 105 |

| 6.4  | BC coverage example of an arithmetic FBD                                  | 106 |

| 6.5  | ICC coverage example of an arithmetic FBD                                 | 106 |

| 6.6  | CCC coverage example of an arithmetic FBD                                 | 106 |

| 6.7  | Addition operator replacement by a multiplier operator                    | 107 |

| 6.8  | Addition operator replacement by a division operator                      | 107 |

| 6.9  | Addition operator replacement by a modulo operator                        | 107 |

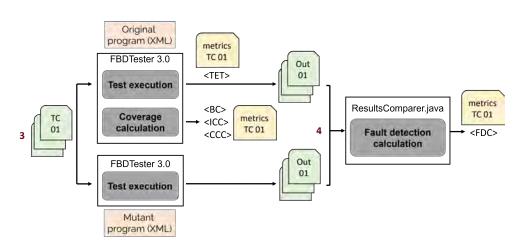

| 6.10 | Test execution and metrics calculation approach                           | 109 |

| 6.11 | Simple non-linear arithmetic FBD program                                  | 13  |

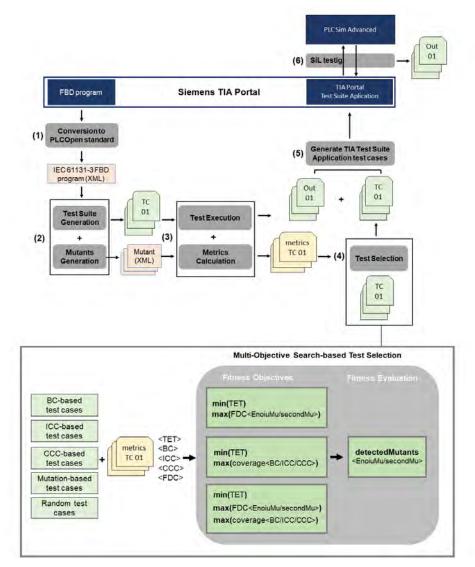

| 7.1  | Cost-effective test selection approach for FBD programs                   | 128 |

| 7.2  | NSGA-II vs RS HV evaluation boxplots                                      | 136 |

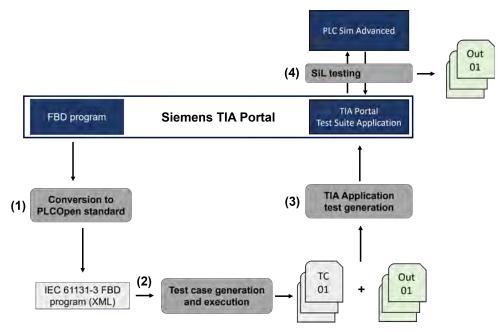

| 8.1  | TIA Portal testing overview                                               | 151 |

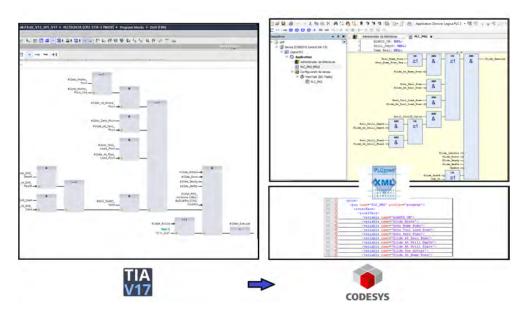

| 8.2  | PLCopen XML conversion via Codesys                                        | 155 |

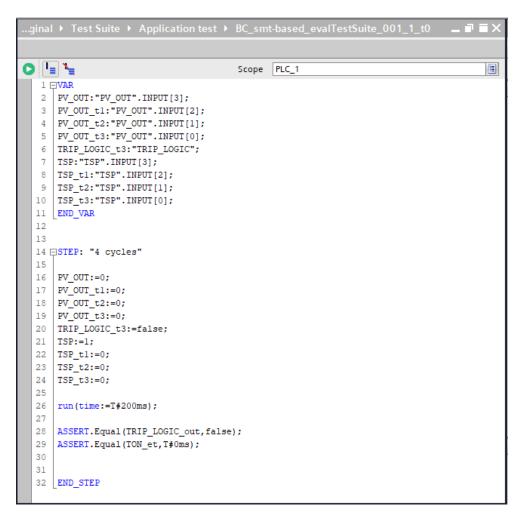

| 8.3  | Example of a TIA Test Suite application test case                         | 157 |

| 8.4  | Successful test execution                                                 | 157 |

| 8.5  | Unsuccessful test execution                                               | 158 |

| 8.6  | Array data types                                                          | 159 |

| 8.7  | First scan network                                                        | 159 |

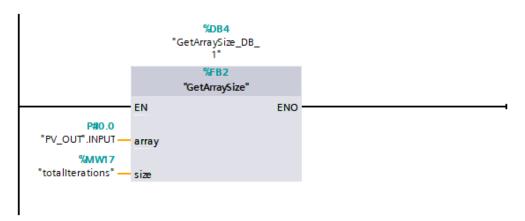

| 8.8  | Get array size network                                                    | 60  |

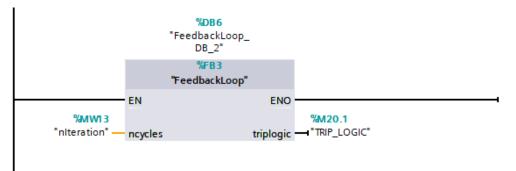

| 8.9  | Feedback loop network                                                     | 60  |

| 8.10 | Reset network                                                             | 161 |

| 8.11 | Main network for FBD unit testing                                         | 161 |

| 8.12 | Safety FBD                                                                | 162 |

| 8.13 | Robot FBD                                                             | 163 |

|------|-----------------------------------------------------------------------|-----|

| 8.14 | TET results a) TET vs number of test cases b) TET vs number of blocks | 167 |

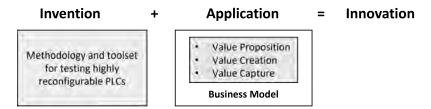

| D.1  | From invention to innovation [MGN19]                                  | 255 |

| D.2  | Integrated Business Model components of our methodology – based on    |     |

|      | [WPUG16b]                                                             | 256 |

# List of Tables

| 2.1  | IEC 61131-3 FC and FB groups                                               | 26  |

|------|----------------------------------------------------------------------------|-----|

| 3.1  | Publications related to digital twin applications                          | 37  |

| 3.2  | Classification of digital twin applications                                | 40  |

| 3.3  | Simulation and emulation tools for virtual commissioning                   | 45  |

| 4.1  | Benefits and challenges of virtual commissioning                           | 66  |

| 4.2  | Benefits and challenges of implementing the digital twin                   | 68  |

| 5.1  | Relationship between objectives, research focuses and gaps                 | 77  |

| 5.2  | Technical contributions and their correspondence to the aforementioned     |     |

|      | steps, objectives, and chapters of the document                            | 83  |

| 5.3  | Omnifactory use case size: number of FBD blocks, inputs, and outputs .     | 85  |

| 5.4  | Danobatgroup use cases size: number of FBD blocks, inputs, and outputs     | 86  |

| 5.5  | KAIST use cases size: number of FBD blocks, inputs, and outputs            | 88  |

| 5.6  | Case studies used to validate each of the contributions                    | 88  |

| 6.1  | Chapter 6 contributions, objectives and hypotheses. Partially related ones |     |

|      | are marked with an asterisk (*) symbol                                     | 92  |

| 6.2  | Yices solver characteristics                                               | 96  |

| 6.3  | Modified statements syntax                                                 | 104 |

| 6.4  | Minimum iteration number of FBs                                            | 108 |

| 6.5  | Example test sequence                                                      | 108 |

| 6.6  | FBD characteristics of the use cases                                       | 114 |

| 6.7  | IEC 61131-3 groups employed in each of the use cases                       | 114 |

| 6.8  | Use cases employed in each of the research questions                       | 115 |

| 6.9  | Coverage-based test cases of LAUNCHER                                      | 116 |

| 6.10 | Coverage-based test cases of simGRAVEL                                     | 116 |

| 6.11 | Coverage-based test cases of FFTD                                          | 117 |

| 6.12 | Mutation test suite size of the use cases                                  | 118 |

|      |                                                                            |     |

| 6.13 | Coverage-based test cases of the non-linear FBD program                           | 118 |

|------|-----------------------------------------------------------------------------------|-----|

| 6.14 | Mutation-based test suite size of arithmetic use cases                            | 119 |

| 6.15 | Non-linear arithmetic mutant operators generated with Yices 2 SMT2 .              | 119 |

| 7.1  | Chapter 7 contributions, objectives and hypotheses                                | 126 |

| 7.2  | Fitness function objectives                                                       | 131 |

| 7.3  | Key characteristics of the selected case studies                                  | 133 |

| 7.4  | p-values and Vargha and Delaney $\hat{A}_{12}$ results based on Romano et al.     |     |

|      | classification, where A=NSGA-II and B=RS. Evaluation with Enoiu et al.            |     |

|      | mutants                                                                           | 137 |

| 7.5  | p-values and Vargha and Delaney $\hat{A}_{12}$ results based on Romano et al.     |     |

|      | classification, where A=NSGA-II and B=RS. Evaluation with second-                 |     |

|      | order mutants                                                                     | 138 |

| 7.6  | Summary of best algorithm results per fitness configuration                       | 138 |

| 7.7  | Vargha and Delaney $\hat{A}_{12}$ values and p-values for the fitness functions – |     |

|      | NSGAII LAUNCHER                                                                   | 139 |

| 7.8  | Vargha and Delaney $\hat{A}_{12}$ values and p-values for the fitness functions – |     |

|      | NSGAII FFTD                                                                       | 141 |

| 7.9  | Vargha and Delaney $\hat{A}_{12}$ values and p-values for the fitness functions – |     |

|      | NSGAII FRTD                                                                       | 142 |

| 7.10 | Cost-effective analysis results of the multi-objective search algorithm vs        |     |

|      | initial test suite                                                                | 143 |

| 7.11 | Summary of results of the most cost-effective metrics                             | 143 |

| 7.12 | Chapter 7 contributions, objectives and hypotheses                                | 145 |

| 8.1  | Chapter 8 contributions, objectives and hypotheses                                | 150 |

| 8.2  | PLCopen XML standardisation alternatives and limitations                          | 154 |

| 8.3  | FBD characteristics of the use cases                                              | 164 |

| 8.4  | Networks used in each of the use cases                                            | 165 |

| 8.5  | Test cases generated for each of the use cases                                    | 166 |

| 8.6  | Test Suite execution results                                                      | 166 |

| 8.7  | Test Suite execution mean values of 50 runs                                       | 166 |

| 8.8  | Application test case mean values of 50 runs                                      | 167 |

| 8.9  | Chapter 7 contributions, objectives and hypotheses                                | 170 |

| 9.1  | Association between contributions and gaps                                        | 175 |

## Acronyms

- ABR Arithmetic Block Replacement

- AMS Autonomous Manufacturing Systems

- AND Logical conjunction operator

- AWL Assembly Language for STEP 7

- BC Basic Coverage

- **BP** Bistable Processor

- C/DC Condition/Decision Coverage

- CC Condition Coverage

- CCC Complex Condition Coverage

- **CNC** Computer Numerical Controls

- CPS Cyber-Physical Systems

- CPU Central Processing Unit

- CTU Count Up operator

- **DB** Data Block of a Function Block Diagram

- **DC** Decision Coverage

- DiManD Digital Manufacturing and Design

- DMS Dedicated Manufacturing Systems

- **DPC** Data Path Condition

- **DSR** Design Science Research

- EAS Evolvable Assembly Systems

- **ERP** Enterprise Resource Planning

- ESR Early State Researcher

- **ET** Execution Time

- FA3D Future Automated Aerospace Assembly Demonstrator

- FAT Factory Acceptance Testing

- FB Function Block of a Function Block Diagram

- FBD Function Block Diagram

- **FC** Function Call of a Function Block Diagram

- **FDC** Fault Detection Capability

- FIO Feedback loop Insertion Operator

- FMS Flexible Manufacturing Systems

- GA Genetic Algorithm

- GE Greater than or Equal to operator

- HiL Hardware-in-the-Loop

- HV Hypervolume indicator

- ICC Input Condition Coverage

- ICT Information and Communications Technology

- IL Instruction List

- IoT Internet of Things

- ITN Innovation and Training Network

- JCR Journal Citation Report

- KAIST Korea Advanced Institute of Science and Technology

- KNICS Korea Nuclear Instrumentation and Control System

- LD Ladder Diagram

- LDO Logical Block Deletion Operator

- LIO Logical Block Insertion Operator

- LRO-I Logical Block Replacement Operator-Improved

- MC/DC Modified Condition/Decision Coverage

- MCC Multiple Condition Coverage

- MCSAT Model Construction Satisfiability algorithm

- MES Manufacturing Execution System

- NSGA-II Non-dominated Sorting Genetic Algorithm II

- **OB** Organisational Block of a Function Block Diagram

- xxvi

- **OR** Logical disjunction operator

- PLC Programmable Logic Controller

- PLM Product Life-cycle Management

- **POU** Program Organisation Unit

- PT Pulse Time

- PTC Propagation Toggle Coverage

- RiL Reality-in-the-Loop

- **RMS** Reconfigurable Manufacturing Systems

- **ROI** Return on Investment

- **RQ** Research Question

- RS Random Search

- RUL Remaining Useful Life

- SAT Site Acceptance Testing

- SBST Search-based Software Testing

- SC Statement Coverage

- SCADA Supervisory Control and Data Acquisition

- SCIE Spanish Informatics Scientific Society

- SCL Structured Control Language

- SiL Software-in-the-Loop

- SMT Satisfiability Modulo Theories

- SMV Symbolic Model Verifier

- **SoS** System of Systems

- SR Set-Reset

- ST Structured Text

- TET Total Execution Time

- TON Timer-on-Delay

- TR Test Requirement

- **TRL** Technology Readiness Level

- UML Unified Modelling Language

- **UNOTT** University of Nottingham

- VRO Variable Replacement Operator

- VRO-I Value Replacement Operator-Improved

- WOS Web of Science

- **XOR** Logical exclusive disjunction operator

Part I

**Foundation and Context**

### Chapter 1

# Introduction

### Contents

\_

| 1.1 | Motiva  | tion and Scope of the Research |  |

|-----|---------|--------------------------------|--|

| 1.2 | Researc | ch Methodology                 |  |

| 1.3 | Technic | cal Contributions              |  |

| 1.4 | Publica | ntions                         |  |

|     | 1.4.1   | Journal Articles               |  |

|     | 1.4.2   | International Conferences      |  |

|     | 1.4.3   | Workshops                      |  |

| 1.5 | Other F | Related Activities             |  |

|     | 1.5.1   | Dissemination                  |  |

|     | 1.5.2   | Service                        |  |

|     | 1.5.3   | Workpackages                   |  |

|     | 1.5.4   | Schools                        |  |

|     | 1.5.5   | Integrated Project             |  |

|     | 1.5.6   | Secondments                    |  |

| 1.6 | Docum   | ent Structure                  |  |

This chapter introduces the motivation and scope of this research work, as well as the issues addressed during the course of the project. The main technical contributions are summarised in Section 1.3, and published research and journal articles are detailed in Section 1.4. Lastly, additional research activities that were carried out are presented in Section 1.5.

### 1.1 Motivation and Scope of the Research

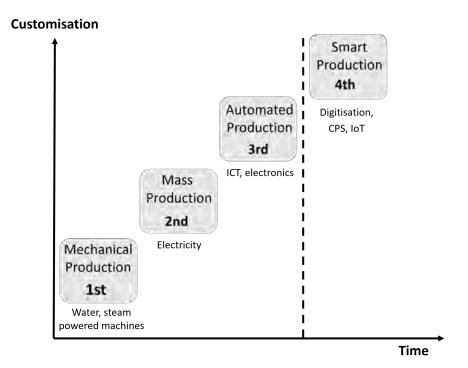

This thesis is part of the Digital Manufacturing and Design (DiManD) Innovation and Training Network (ITN) programme, which is a high-quality multidisciplinary, multi-professional, and cross-sectorial European research and training network focused on Industry 4.0. The main objective is to foster industrial competitiveness and sustainability in the European manufacturing sector, by leveraging a technology-driven infrastructure that can produce a wide range of dependable products in a cost-effective manner. In effect, this program promotes a new way of manufacturing high-quality goods whilst complying with sustainable development goals throughout the whole life cycle of the product.

Present-day manufacturing is undergoing a shift from the traditional mass productionbased paradigm to offering customised products. To respond to ever-changing customer needs, production systems must be highly reconfigurable and adaptive. Instead of solely focusing on specific tasks, these systems need to deliver a wider variety of products with rapid turn-around. A critical attribute to succeed in this transition is agility.

Adaptive manufacturing systems require re-configuring the existing layout, adding new elements, and modifying or removing existing ones based on the needs of the moment. Most of these reconfigurations involve changes in the manufacturing process, and orchestration is thus a complex and crucial task. PLCs are commonly used to control industrial manufacturing processes, and these must be adapted to orchestrate new processes in the manufacturing system. Every change in the PLC code must be fully tested, however, to ensure there are no errors before being deployed into operations. At present PLC testing is mostly conducted manually. This is a tedious task which demands considerable time and effort, and is highly error-prone. The problem is further compounded in reconfigurable and adaptive production systems, as these continuously undergo changes which require rigorous testing before implementation.

Cyber-Physical Systems (CPS), which include PLCs, are traditionally tested during the commissioning phase of the development process. This is not ideal, as commissioning occurs at the very end of the chain-based manufacturing process, in which each step depends on the previous one (design -> planning -> engineering -> assembly -> commissioning). Despite the evident logic of this structure, any unexpected issue in any of these steps can result in serious delays in downstream processes. Hence, commissioning at the end of the development process can incur significant costs, as the system is not tested until everything is in place.

The advent of Industry 4.0 has placed virtual commissioning centre stage, as a series of verification tasks between multiple engineering disciplines can be instigated early in the development process. This has obvious benefits in that it can significantly reduce commissioning time, errors, and costs. This potential remains under-exploited in industry, however, as virtual commissioning is still rarely applied until the latter stages of the manufacturing chain.

In the manufacturing sector companies are reluctant to invest in simulation technologies for virtual commissioning [UQEESM<sup>+</sup>21, LP14, KWL<sup>+</sup>20]. This is particularly true of machine tool manufacturers. One of the main issues is interoperability: each vendor delivers a single solution with proprietary communication protocols, thereby limiting the integration of other products. Integrating simulation tools from different domains, as well as the numeric controller to perform virtual commissioning, only serves to exacerbate the problem. Moreover, virtual models may lack accuracy, as they do not reflect the conditions of physical devices, and require additional validation to be performed through conventional commissioning procedures. As a result, companies are unable to justify the Return on Investment (ROI), which poses a serious obstacle to the adoption of virtual solution strategies.

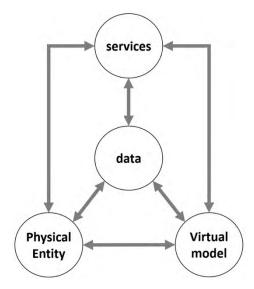

Digital twins are thus well positioned to enhance virtual commissioning practices as they can address synchronisation issues and misalignments between virtual representations and the physical system. In addition, while virtual commissioning typically consists of various simulation technologies commissioned in silos by distinct engineering disciplines, the digital twin can integrate all these models into a single framework. However, no commercial holistic and multi-domain solution technologies are currently available.

Agile testing methodologies which exploit the virtual commissioning framework are critical to maintaining a competitive edge in European manufacturing. These include methods to detect defects, malfunctioning, and potential errors in the design. These can save time, resources, and overall costs by preventing corrections in the commissioning stage.

To overcome the gap in integrating software testing techniques in industrial environments, the following challenges need to be first addressed:

■ Ch1: dealing with turbulent and competitive markets.

#### 1. INTRODUCTION

- Ch2: fostering sustainable goals.

- Ch3: interoperability issues due to vendor proprietary protocols and languages.

- Ch4: time to market and costs as a result of commissioning at latter stages of the development process.

- Ch5: lack of collaborative and holistic solutions for virtual commissioning, in which different multi-domain disciplines can work collaboratively.

- **Ch6:** difficulty in quantifying the ROI.

- Ch7: time and effort required to test and commission PLCs, which are further increased in adaptive manufacturing systems.

- **Ch8:** dealing with frequent errors as manual testing is error-prone.

- Ch9: lack of knowledge transfer to industrial environments.

In light of the issues identified above, this research project focuses on providing an agile mechanism to test industrial PLC programs based on software engineering practices (*Ch9*). To accomplish this, we propose a theoretical virtual commissioning framework (*Ch3*, *Ch5*) to foster the continuous integration of PLC software (*Ch7*). Our work is aligned with the objectives of DiManD, and the methodology we present provides an automated (*Ch8*) cost-effective (*Ch6*, *Ch7*) approach for testing PLC programs that are subject to frequent reconfigurations (*Ch1*). Our approach maximises the use of existing manufacturing resources (*Ch2*) and delivers high reliability while reducing commissioning time (*Ch4*).

## 1.2 Research Methodology

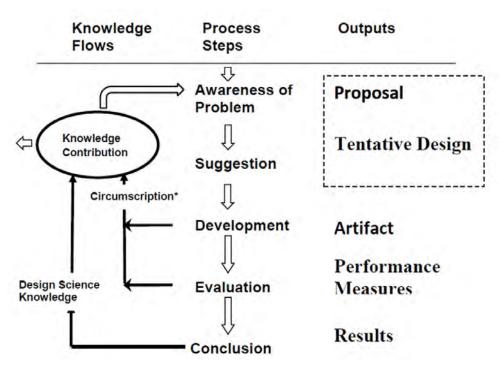

The research methodology follows the guidelines of the Design Science Research (DSR) framework presented by Vaishnavi et al. [VK15]. The methodology comprises a five steps process, as indicated in Figure 1.1.

Awareness of problem: the first step is the acknowledgements of a problem. In this case, the initial problem could be used to tackle a research question. The output might be a formal or informal proposal. To this end, with the aim of increasing awareness and obtaining a comprehensive understanding of the problem, an extensive literature review was conducted (Chapter 3). In addition, we supplemented our findings with an industrial survey to obtain further insights regarding the research

Figure 1.1: General overview of the research methodology [VK15]

questions we posed about virtual commissioning practices in the manufacturing industry (Chapter 4).

- Suggestion: in this step, a tentative solution is suggested to address the initial problem. The suggestion might come from the existing knowledge, and is usually an integral part of a formal proposal. In response to the identified gaps, we proposed a theoretical framework and suggested 4 hypotheses (Chapter 5), including a hypothesis related to the theoretical framework, and three technical.

- Development: development and implementation of the suggested tentative solution. As a result, a novel artefact is created. Specifically, we developed three technical artefacts to address the technical hypothesis raised in the previous step. These artifacts are described in Chapter 6, Chapter 7 and Chapter 8.

- Evaluation: in this step, the partially or fully implemented artefact is assessed based on certain criteria. This phase involves an analytical subphase, where the hypotheses are tested, and the resulting knowledge is looped back to the previous stages. To this end, we carried out an empirical analysis to evaluate each of the technical artefacts and thus, respond to the hypotheses. These were individually evaluated in the corresponding chapter.

Conclusion: the research cycle finishes when the resulting artefact complies with the requirements specified in the previous phases. The knowledge gained within this process is fed back for the next research cycle. In this case, we used all this knowledge to present a business model (Section D.2) of the developed solution, with the aim of assessing the impact of our proposal in the market.

## **1.3 Technical Contributions**

In this thesis, we present a methodology to cost-effectively test industrial PLC programs with the aim of reducing commissioning time, while ensuring a high level of reliability. The ultimate goal is to maximise the reuse of manufacturing resources to address new bills of process, by promoting the continuous integration of PLCs. To this end, we introduce a theoretical framework for virtual commissioning. Our simulationbased approach automatically tests Siemens PLCs – one of the most widely used in industry – by applying software engineering techniques to commercially available automation solutions. The main contributions of this thesis are summarised as follows:

- Preliminary work: an empirical survey to identify industrial requirements, challenges, and needs. This process involved industrial and academic stakeholders, and provided first-hand information on virtual commissioning practices. The results of the study were supported with an expanded review of the literature to pinpoint emerging trends and research gaps.

- 2. **Theoretical framework:** a theoretical virtual commissioning framework designed to address the identified industrial needs, which ultimately could facilitate the continuous integration of PLCs in the ever-changing manufacturing field.

- 3. Technical contribution 1: a test case generation and evaluation approach for IEC 61131-3 FBD programs. Effectively, the approach included coverage-based, mutation-based, and random test cases. This was achieved by extending the capabilities of existing tools and incorporating a new solver capable of handling a broad range of IEC 61131-3 FBD programs, including non-linear arithmetic functions. We also developed an automated test evaluation approach, in which cost-effective metrics were calculated, and test oracles were obtained from test execution results. The metrics are used to optimise test selection, whereas test oracles are employed to validate the simulation results.

- 4. **Technical contribution 2:** a cost-effective test selection approach. To this end, we implemented a search-based test selection algorithm to optimise the selection of

test cases. The optimisation focused on maximising fault detection capability while minimising execution time. This was accomplished by defining a fitness function based on the derived cost-effective metrics, which included coverage, execution time, and fault detection capability.

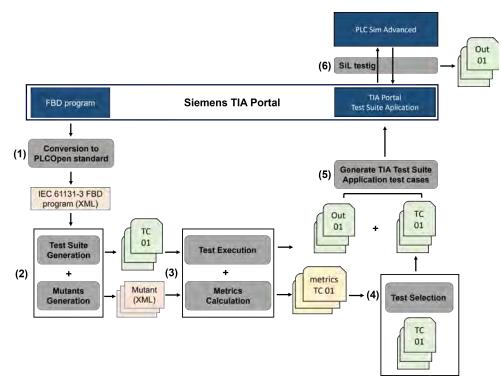

5. Technical contribution 3: a methodology to test Siemens PLC programs. The solution is based on a Software-in-the-Loop (SiL) approach, which uses the Siemens automation platform – TIA Portal – to perform the tests against the Siemens virtual controller. Test oracles were used to assert the results of the simulation. The methodology comprised six steps, including 1) PLC code standardisation, 2) test case generation, 3) test case evaluation, 4) test case selection, 5) TIA Portal application test generation, and 6) simulation-based application test execution.

## 1.4 Publications

In total, five peer-reviewed publications were published in journals and at conferences during the course of this project. At the time of writing, a further two articles were under review, and one final article was ready for submission.

The publications are scored according to the Journal Citation Report (JCR) from Web of Science, CiteScore from Scopus, and Scimago Journal Rank (SJR) from Scimago. In addition, the conference publication papers related to software engineering are ranked by the ranking systems supported by the Spanish Informatics Scientific Society (SCIE (www.scie.es)).<sup>1</sup>

## 1.4.1 Journal Articles

During the course of this dissertation, two journal articles were published:

- Miriam Ugarte Querejeta, Leire Etxeberria, Goiuria Sagardui, Gorka Unamuno, and Iñigo Bediaga. "Virtual commissioning in machine tool manufacturing: a survey from industry" in DYNA Ingeniería e Industria (2021), 96 (6), pp. 612-619.

JCR: 2.070 Engineeering Multidisciplinary Q3 51/92. SJR: 0.160 Engineering C4 333/414 2021 2022-07-11. CiteScore 1.3: General Engineering CS3 178/300.

- Miriam Ugarte Querejeta, Miren Illarramendi Rezabal, Gorka Unamuno, Jose Luis Bellanco, Eneko Ugalde, and Antonio Valor Valor. "Implementation of a holistic digital twin solution for design prototyping and virtual commissioning". IET Collaborative Intelligent Manufacturing (2022), vol. 4 (4), pp. 326-335. SJR:

<sup>&</sup>lt;sup>1</sup>http://gii-grin-scie-rating.scie.es/

0.568 Industrial and Manufacturing Engineering C2 104/368. **CiteScore:** 2.8. Industrial and Manufacturing Engineering C3 151/338.

At the time of submitting this thesis, a journal article was also in progress for later submission to the Journal of Manufacturing Systems.

Fan Mo, Miriam Ugarte Querejeta, Joseph Hellewell, Hamood Ur Rehman, Miren Illarramendi Rezabal, Jack C. Chaplin, David Sanderson, Svetan Ratchev. "PLC Orchestration Automation to enhance Human-Machine Integration in Adaptive Manufacturing Systems". JCR: 9.498 Engineering, Manufacturing Q1 7/51.

In addition, as part of the work carried out in the workpackages within the DiManD network, a journal article was sent for review in the Journal of Intelligent Manufacturing, which has been accepted for publication:

Jose Antonio Mulet Alberola, Luis Alberto Estrada-Jimenez, Hien Nguyen Ngoc, Trunal Patil, Miriam Ugarte Querejeta, Angela Carrera-Rivera, Mauro Onori and Antonio Maffei. "Towards autonomous manufacturing automation: Analysis of the requirements of self-x behaviours". JCR: 7.136 Engineering, Manufacturing Q1 11/51.

## 1.4.2 International Conferences

Two international conference articles were published at ISM and CIRP:

- Miriam Ugarte, Leire Etxeberria, Gorka Unamuno, Jose Luis Bellanco, and Eneko Ugalde. "Implementation of Digital Twin-based Virtual Commissioning in Machine Tool Manufacturing" in Procedia Computer Science (2022), 200, pp.527-536. CiteScore: 3.0 General Computer Science CS2 71/226.

- Itziar Ricondo, Alain Porto, <u>Miriam Ugarte</u>. "A digital twin framework for the simulation and optimisation of production systems" in Procedia CIRP (2021), vol. 104, pp. 762-767. CiteScore: 3.3 Industrial and Manufacturing Engineering CS2 107/336.

Furthermore, at the time of submitting this thesis a conference paper was sent for review by the Genetic and Evolutionary Computation Conference (GECCO 2023).

Miriam Ugarte Querejeta, Pablo Valle, Aitor Arrieta, Eunkyoung Jee, Lingjun Liu, Miren Illarramendi Rezabal. "Cost-Effective Test Selection for Functional Block Diagram Programs". SCIE: A.

## 1.4.3 Workshops

A conference article was published at the SAFECOMP-DepDevOps workshop.

Miriam Ugarte Querejeta, Leire Etxeberria, and Goiuria Sagardui. "Towards a DevOps Approach in Cyber Physical Production Systems Using Digital Twins" at the International Conference on Computer Safety, Reliability, and Security (2020), pp. 205–216. SCIE: B-.

## 1.5 Other Related Activities

In addition, the PhD student has contributed to other activities that furthered her training and professional development as a researcher. These activities included dissemination activities, service to the community, participation in DiManD schools, national and international secondments, and work in collaborative workpackages within the DiManD project.

## 1.5.1 Dissemination

The work developed during this research project, as well as the DiManD project, were disseminated in the following events:

- DiManD project dissemination within the R&D Projects Dissemination Event at the 3rd International Conference on Industry 4.0 and Smart Manufacturing (ISM 2021).

- Roundtable in the STEAM Technology and Science Week at GARAIA Technology Park (2020).

- Short video recording on digital twins and Industry 4.0 for the Citizen Engagement Event (2020).

- Thesis and DiManD project presentation at MGEP as part of the NiZuGu Mugituz career counselling project.

- Short video interview that describes this research project within the scope of the DiManD project, published on the <u>www.dimanditn.eu</u> webpage.

- Short video recording that describes this research project as part of the DiManD project on the Mondragon Uniberstitatea, Faculty of Engineering communication channel (2022).

## 1.5.2 Service

The PhD student was involved in the following activities as service to the research community:

- Early State Researchers (ESRs) delegate on the DiManD supervisory board.

- Peer-reviewer at the 3rd International Conference on Industry 4.0 and Smart Manufacturing (ISM 2021).

## 1.5.3 Workpackages

Complementary research was carried out in several multidisciplinary work packages, within the framework of the DiManD programme. This contributes to an inter-sectoral and interdisciplinary collaborative framework, which facilitates cooperation, communication, and teamwork among all participants. In particular, the PhD student was involved in WP3 Tasks 3.1 and 3.2, and WP4 Tasks 4.2 and 4.3. The outcomes are published at <u>www.dimanditn.eu</u>.

**WP3:** Integration of computation, networking, and physical processes into CPS. This workpackage was led by KTH Royal Institute of Technology.

- Task 3.1: Identification of major challenges to the industrial adoption of CPS focusing on the integration of computation, networking and physical processes towards the vision of CPS.

- Task 3.2: Development of a CPS architecture that provides the necessary framework for the development of CPS.

As part of Task 3.1, a comprehensive state-of-the-art analysis was conducted within the field of autonomous CPS, Circular Manufacturing Systems, and Evolvable Production Systems. Further research was also focused on Self-X behaviours, such as self-adaptation, self-configuration, self-organisation, and self-learning to establish the requirements of the CPS architecture.

Task 3.2 involved Quality Function Deployment methods focusing on the requirements established in Task D3.1, as a mechanism to measure the requirements to form the new paradigm. The technical requirements were therefore prioritised and mapped onto the 5 CPPS architecture and MAPE-K loop to build the new paradigm of autonomous and sustainable manufacturing systems. **WP4:** Autonomous, context aware manufacturing platforms. This workpackage was led by the University of Nottingham.

- **Task 4.2**: Development of a data model for proactive intelligent products.

- Task 4.3: Development of adaption strategies for context-aware autonomous systems.

As an outcome of Task 4.2, two data models were designed: 1) a process data model to represent manufacturing process requirements and production knowledge, and 2) a runtime condition model to represent the capabilities and status of manufacturing resources. The main objective was to develop an intelligent product that could potentially produce a new bill of process by matching these two data models.

Finally, the scope of Task 4.3 was to define an adaption strategy to reschedule tasks in the event of unforeseen situations. This was carried out based on the data models developed in Task 4.2.

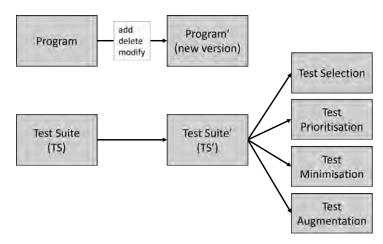

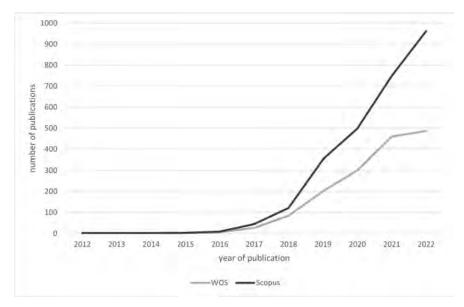

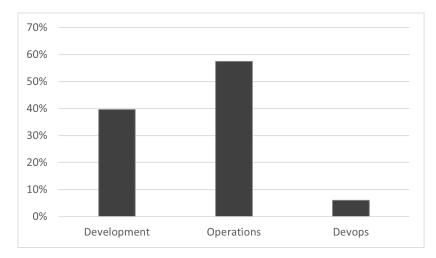

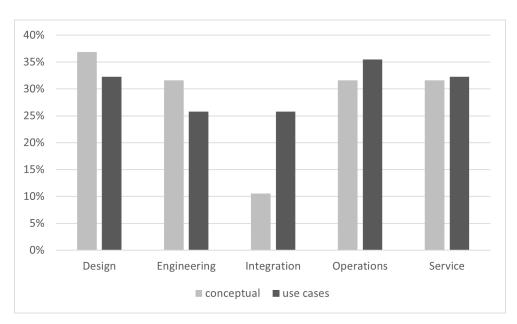

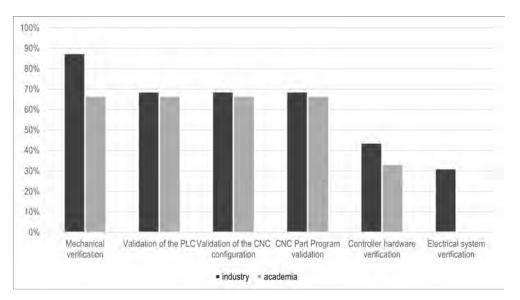

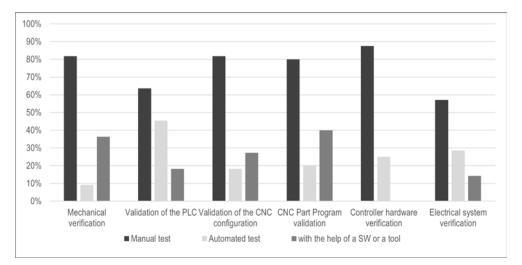

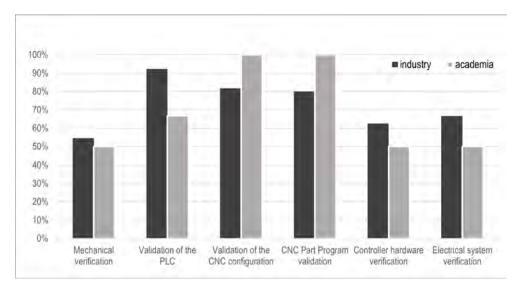

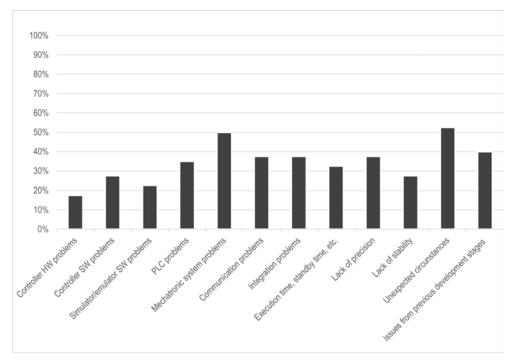

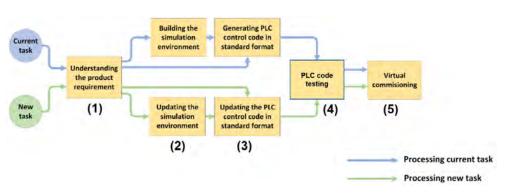

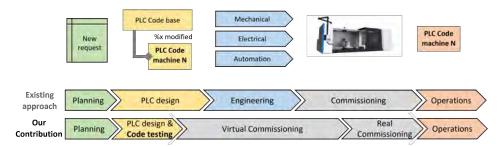

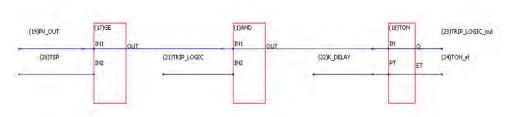

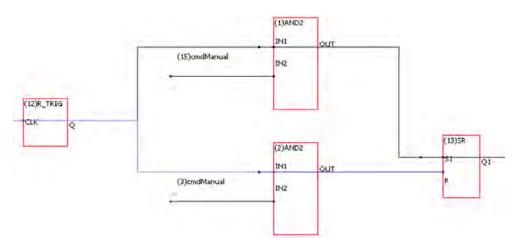

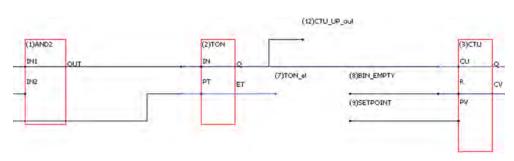

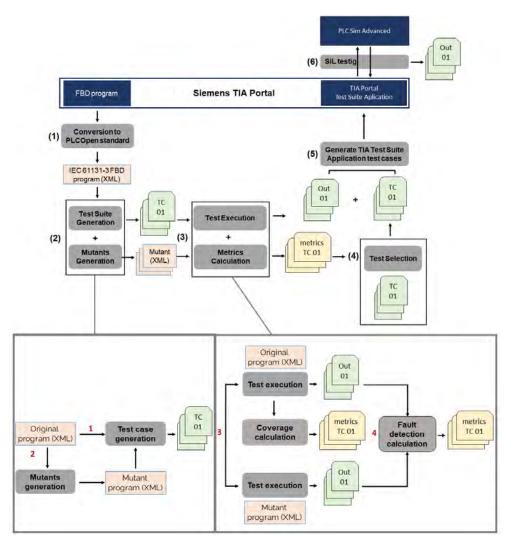

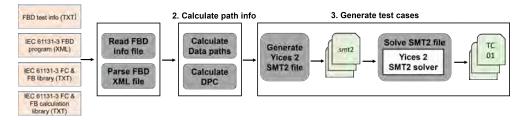

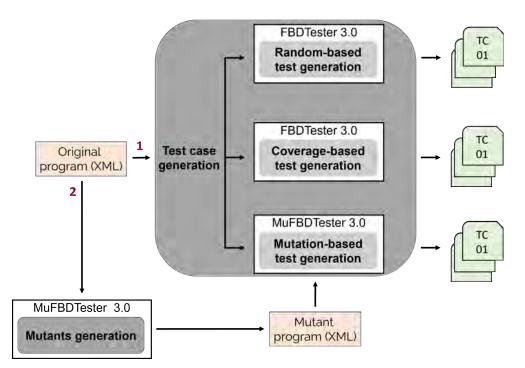

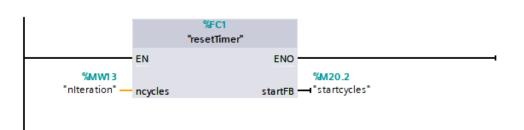

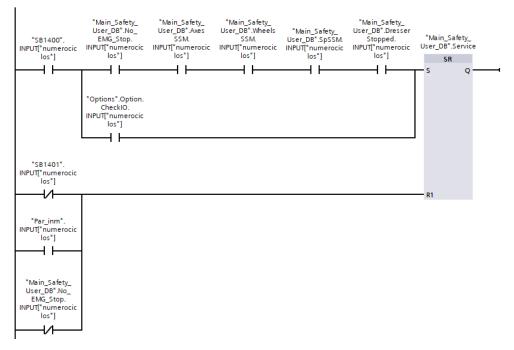

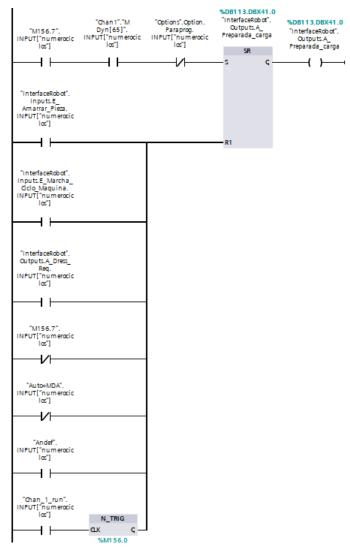

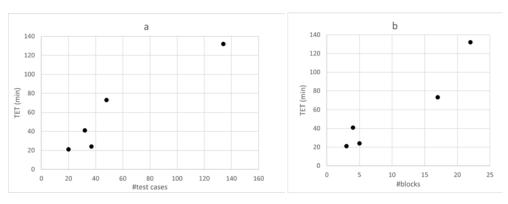

## 1.5.4 Schools